如何将反相器改装为运算放大器的设计

品慧电子讯社会发展和科技进步,人们小巧、高效CPU的青睐,促使互补式金属氧化物半导体(CMOS)的制造工艺达到了纳米级。随之出现的问题是这些精良制造工艺对电源缩放和器件漏电等给精密模拟电路带来了不利影响,本设计实例对具备真正差分输入和近似轨到轨输出摆幅能力的二级运算放大器(通过5V单电源供电)进行演示。

本设计实例对具备真正差分输入和近似轨到轨输出摆幅能力的二级运算放大器(通过5V单电源供电)进行演示。 人们对更小巧、更高效CPU的青睐,促使互补式金属氧化物半导体(CMOS)的制造工艺达到了纳米级。但这些精良制造工艺涉及的电源缩放和器件漏电等问题给精密模拟电路带来了不利影响,致使研究人员需要开发可以实现传统模拟密集型功能的高度数字化替代性架构。模拟域的“数字化”将最终延伸至广大的业余爱好者,他们将越来越难找到简单的模拟器件。

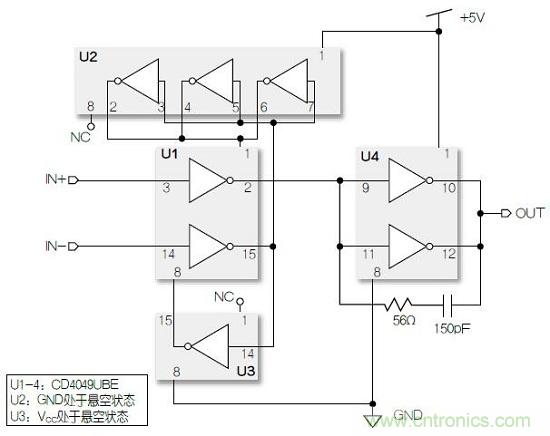

图1显示的是一个二级运算放大器的完整实现,该运算放大器仅使用了四个CD4049UBE六反相器、一个电阻器和一个电容器(参考文献4)。请注意,图中U2的引脚8(GND)处于悬空状态,而U3的引脚1(VCC)也处于悬空状态。U2中的并联反相器的输出端与U1的VCC引脚相连,而U3中的反相器的输出端则与U1的GND引脚相连。

图1:二级运算放大器的完整实现。

图2显示的最终电路的晶体管级功能原理图,该电路的外部晶体管已被移除。电路的第一级取自参考文献5中的电路,以实现从差分到单端的转换。U2反相器内的P沟道金属氧化物半导体(PMOS)器件充当电流源,而U3反相器内的N沟道金属氧化物半导体(NMOS)则作为电流阱。由于PMOS和NMOS的强度不对等,在过去所采用的方法是用不同数量的电流源和电流阱把共模范围拉伸至中等大小。

图2:晶体管级功能原理图。

12下一页>

- 第一页:如何将反相器改装为运算放大器的设计

- 第二页:如何将反相器改装为运算放大器的设计

U1中的变频器充当双gm差分对。因为电路的第一级仅有介于25dB和30dB之间的增益,故增加了第二级。由于两级的带宽类似,因此采用标准补偿技术来保证整体的稳定性。请注意,任何合理的反馈组态都必然会将第二级带入线性范围,由此无需应用可减少增益的局部分流电阻器。

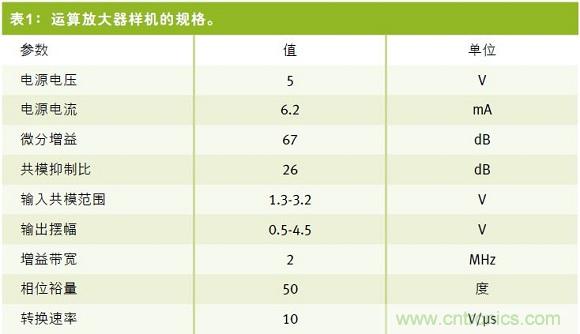

表1中列出了运算放大器原型的大致规格。尽管运算放大器有差分输入,但并没有太大的共模抑制。从另一方面来说,该运算放大器的增益带宽要大于典型的LM741运算放大器的增益带宽。

该设计若采用CD4069UB和74HCU04这两种器件应当能够同样好地工作,尽管U2和U3中器件的比率可能会改变,从而使具有不同驱动强度的晶体管的共模范围重新回到中心位置。而唯一的关键点是反相器是无缓冲的,否则每个增益级会变成一个三级环形振荡器。

图3:测得的开环放大器的增益幅度响应。

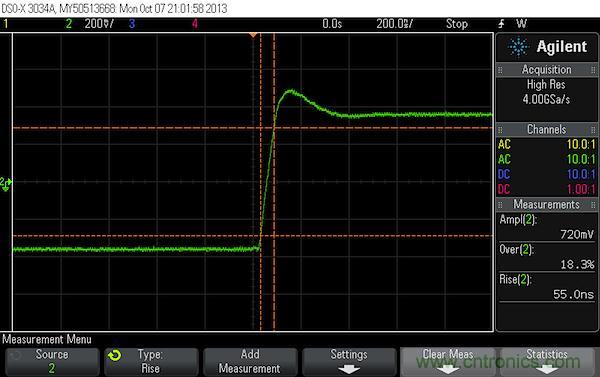

图4:电压缓冲器组态的大信号阶跃响应,显示了带有缺陷的零点取消的某些过冲特点。

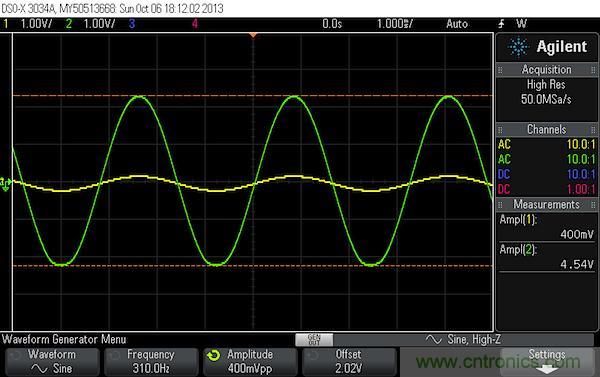

图5:基于5V单电源的接近实际应用的轨到轨运行(运算放大器配置的非反相增益为11)。

图6:用万用板制成的原型。