基于RF DAC的电缆系统下游发射机设计

从2003年至今,电缆服务宽带数据订阅用户数量的复合年增长率接近14%,并且增长趋势没有放缓,而要想在消费者数据需求增长的环境下保持领先地位,电缆服务提供商需要升级其分配系统。本文介绍的电缆系统下游发射机设计也许是个不错的参考。

过去十年间,电缆系统中使用的宽带数据数量增长迅猛。从2003年起,电缆服务宽带数据订阅用户数量的复合年增长率接近14%。近年来,数据使用增长的趋势没有出现放缓的迹象,因为越来越多的消费者使用基于网络的服务来实现视频流、音频流和游戏应用。

电缆服务提供商正在升级其分配系统,从而在消费者数据需求增长的环境下保持领先地位。传输系统的本质是从多址传送系统发展成多址传送和窄播相结合的系统,前者向所有的订阅者都发送相同的信号,后者中有些内容由所有订阅者共享,有些内容直接发送至特定的订阅者。

电缆系统下游发射机

数字电缆发射机已从传统发射机发展到直接调制技术,传统发射机中的一对基带DAC用来驱动正交调制器,正交调制器的本振用来选择正确的RF频率。

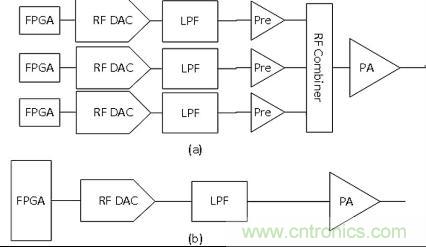

在直接调制发射机中使用了一个RF DAC,电缆通道全部创建在数字域中,通常为FPGA。数字信号从FPGA发送至RF DAC,将其转换成模拟信号然后发送至功率放大器。典型电缆发射机的简化框图如图1所示。

图1(a):使用多个RF DAC和一个RF合成器实现完整电缆频谱的典型电缆发射机框图

(b):使用新型AD9129 RF DAC的新型电缆发射机框图在图1(a)中,发射机由几个RF DAC组成,这些RF DAC由几个FPGA驱动,然后每个RF DAC的输出发送至前置放大器。前置放大器的输出组合后反馈至驱动电缆设备的单个功率放大器。使用该架构的原因是,以合理功耗来综合大量数字信号的FPGA的栅极数量和容量是有限的,而且每个RF链都可以针对特定频带进行优化。

RF DAC通常具有信号处理功能,可以限制可能产生的总RF带宽,但可以减少FPGA的接口要求。上一代RF DAC具有良好的性能,但谐波性能不能满足严格的DOCSIS规格,因此需要进行细致的频率规划和RF滤波器设计才能达到可接受的性能。

其架构可能采用每个RF DAC 2、4或8个256-QAM通道,虽然需要耗费额外的硬件成本,但可以提供可扩展性。该架构存在若干不足之处。随着所需通道数量的增加,RF合成器变得更加复杂,随着每个DAC通道的增加,合成器的损耗也会增加。

每个FPGA+RF DAC+前置放大器链的功耗很大,可能达到每通道10 W。所需的多个RF链可能需要多卡来实现158通道的完整电缆频谱,每张卡的功耗为1 kW或更高。在一个设备中安放多张卡是为1000户的群组提供服务所必需的。

系统变得很大,需要多张卡才能为每个1000户的群组提供服务。因此需要大型设施或建筑将所有的卡安放在大型机架或机壳中,必须特别注意机架冷却系统,将建筑保持在适当的工作温度所需的费用也很高。

如今,由于栅极数量的增加和细线CMOS工艺的出现,FPGA可以实现足够高的密度,从而在FPGA(驱动一个RFDAC)上创建整个1586MHz宽电缆通道。结合ADI公司的新型AD9129 RFDAC后,可以设计出更加简化的电缆发射机。

图1(b)显示的是新型发射机的框图,这种发射机能够合成50MHz~1GHz的整个下游电缆频谱。FPGA中的数字调制器以2.8GSPS的高采样速率驱动AD9129 RFDAC。

DAC具有一个可选2倍插值器滤波器,可以用来实现带外元件的片上数字滤波,可将有效采样速率提高到5.6GSPS。DAC输出采用低通滤波器进行滤波,并从Triquint TAT2814发送至新的高度集成的可变增益放大器和驱动放大器。

放大器将前置放大器、可变衰减器和驱动器放大器集成在一个模块中,实现了新的集成水平。这使得无线电部分的布局变得紧凑,并减小了每个无线电端口的物理尺寸。

设计示例

1、RF DAC

AD9129 RFDAC的采样速率高达2.8GSPS。这种高采样速率的优点在于,DAC镜像折叠比之前的解决方案高fDAC/2。这可以防止镜像在600MHz下折叠,从而降低其抑制要求。数据通过时钟频率为700MHz的双LVDS端口传输至DAC,数据输入至时钟的两个边沿,每个端口上的数据传输速率为1.4GHz。

DAC的电流驱动架构和细致设计可以实现出色的杂散性能和噪底。DAC采用0.18μm工艺,使得功耗降至约1.1W。

2、低通滤波器

在DAC和放大器之间,无源信号调理有助于满足DOCSIS规格,实现所需的带外抑制比和功率波动。设计示例中选用了七阶椭圆滤波器来解决带外抑制问题。AD9129DAC的2.305 GSPS低采样速率用来评估低通滤波器带外性能,因为镜像在低采样速率时折叠在离电缆带更近的位置。

1GHz通道的镜像需要特别注意,因为它落在1.3GHz的位置,离所需信号仅300 MHz。该设计针对1.3GHz镜像达到了62.5dBc的镜像抑制,符合DOCSIS规格对于带外抑制比要求。两个串联谐振均衡器用来解决电缆带上由于DAC输出上的sinc滚降和功率放大器中的额外滚降造成的功率波动问题。均衡器在电缆带中的最高功率通道和最低功率通道之间达到的功率波动约1.4dB,满足DOCSIS规格,无需任何输入信号的数字操控。每个独立通道的功率都可以进行数字调整,以便在电缆带上实现更加精细的调谐平坦度。

3、输出放大器

TAT2814输出放大器将三项功能合并在一个封装内,大大降低了电路板空间,具有高集成度。这款放大器可能达到的总增益约30dB。输出能够为1通道256-QAM信号提供高达+65dBmV的功率。放大器在GaAs工艺中实现,并针对低功耗进行了优化。该集成器件的总功耗约4.2W。

4、非线性校正

非线性校正(NLC)用来改进整个信号链的带内谐波性能,校正来自DAC和功率放大器的失真,以及可能沿信号链产生的其他失真。NLC过程可以进行编程设置,以使电路板满足规格要求,或留出指定的裕量,以允许制造容差。NLC校准仅需几分钟,可大大改进系统性能。

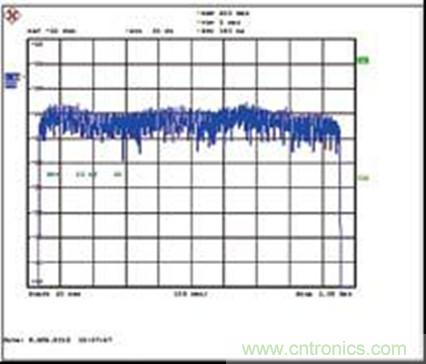

图2:设计示例输出端158DOCSIS256-QAM通道的整个电缆带

5、测量结果我们用AD9129设计了一块优化布局的电路板,并测量了其性能。具有所有158个通道的信号用来测试电缆带上的电路板响应平坦度。图2所示为以整个频带信号作为输入的优化电路板输出。最高和最低功率通道之间的功率波动仅约1.4dB,在DOCSIS规格内,且能够通过数字操作输入信号进一步改进。

测试显示,电路板可以用4dB裕量来可靠校正,使系统在制造容差内保持稳定。