提高同步整流应用的系统效率和功率密度

中心议题:

- 系统效率和功率密度的重要性

- 同步整流中的驱动损耗

- 飞兆半导体领先的RDS(ON)性能

- 同步整流中的电压尖刺损耗

解决方案:

- 屏蔽栅极技术

- 提高同步整流应用的系统效率和功率密度的应用方案

随着功率电源技术和信息技术的发展,用户对高效率小体积产品的要求越来越高,对电源的性能也相应提出了更为苛刻的规范要求,电源市场迎来巨大的商机,同时也迎来了巨大的挑战。本次报告包括以下几项内容:系统效率和功率密度的重要性,行业发展的趋势以及相应的解决方案,电源设计中面临的挑战,需要更高系统效率和功率密度的一些典型应用,以及在选用飞兆半导体采用屏蔽技术的中等电压Power Trench MOSFET后可实现更高系统效率和功率密度。

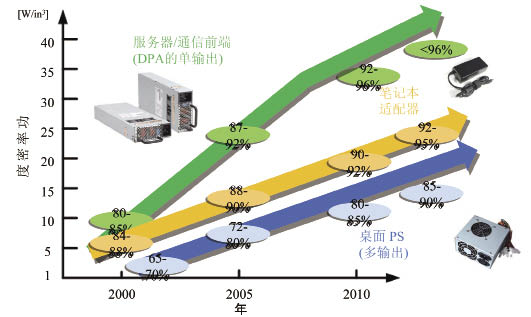

基于系统效率和功率密度发展趋势示意图,我们可以清晰的看出,在最近的十年间系统的效率和功率密度有了巨大的提升,尤其以服务器和通信电源为显著。这一巨大的提升是如何实现的呢?它主要是通过尝试新的拓扑结构,引进新技术高性能的功率器件,同时通过良好的系统设计来保证,以上几点我们会在接下来的内容中给出进一步的讨论。

系统效率和功率密度的重要性

为了说明系统效率和功率密度的重要性,我们以通信网络能耗增长为例做简要介绍。自2009年开始,通信网络每年的能耗百分比都以线性上升,到2016年这一数字将翻番,这彰显了系统的效率和功率密度对于工业应用是多么重要。

随着对电源系统效率和功率密度不断提高的行业发展趋势,各个国家和地区针对自己的具体情况开发并颁布了一系列新的标准以适应本国情况,例如美国的能源之星、欧盟的生态标准以及中国的CSC标准。电源行业针对这些新的要求,通过提高系统效率,增加功率密度及降低能源成本的方式来达到新标准的要求。

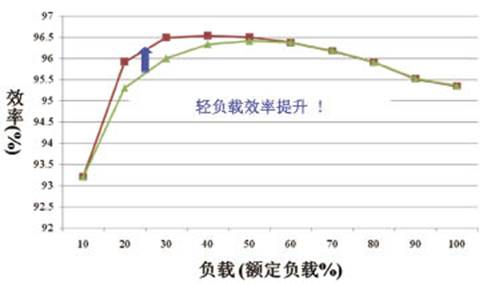

针对于服务器应用和通信应用的高性能电源,在设计过程中有以下三个指标尤为重要:一、如何提高系统的功率密度,二、如何提高系统轻载下的效率,三、如何实现长系统寿命下的高可靠性。图片所示是在原系统基础上改用飞兆半导体中等电压Power Trench MOSFET后在轻载25%状态下效率有明显的提高,大约1%左右。

系统效率和功率密度发展趋势示意图

飞兆半导体应用解决方案

针对目前高性能电源设计中的难点,飞兆半导体的解决方案可以帮助客户降低系统的RDS(ON),减少系统的传导损耗,减少系统的开关噪声,以及减少系统的热耗散,从而使得单位面积做到最小。除了通信电源以及服务器电源之外,需要更高效率和功率密度的应用还有很多,例如ATX电源以及专事转换器、VRM模块、D类音频放大器以及马达驱动等。

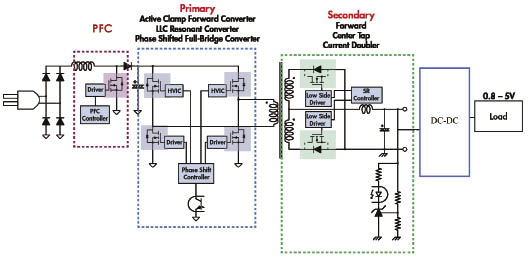

这里我们首先以AC-DC同步整流应用为例。在通讯电源的应用中它的主功率部分主要由功率校正电路、原边的电源转换电路、副边的整流电路组成,我们可以很清楚的看到,在图中有非常多的功率器件,系统的效率也就由这些功率器件的工作效率以及本身的性能优劣决定。

在服务器中隔离型或非隔离型DC-DC电路的应用,我们可以用方框图来描述。在下方蓝色图中是一典型的服务器电源的组成架构,它由原边、副边以及非隔离型的DC-DC电路组成。如通信电源一样,在其中有非常多的功率器件来实现电流、电压的转换电路,使系统的效率高低以及功率密度可以做的好坏和功率器件的选择有着直接和密不可分的关系。在以上描述的功率转换电路中,选择飞兆半导体采用屏蔽栅极技术的中等电压Power Trench MOSFET之后,可以实现系统的更高效率和更高的功率密度。

123下一页> 关键字:同步整流 屏蔽 整流 RDS(ON) MOSFET 本文链接:http://www.cntronics.com/public/art/artinfo/id/80014134

屏蔽栅极技术

这里我们对沟槽型功率MOS管的发展做一个简单的回顾。左边是传统沟槽型MOSFET的典型结构,与前期的平面结构的MOS管相比,它具有更低的RDS(ON)以及更好的开关特性。经过一段时间的发展,底部有厚氧化层的沟槽型MOS管替代了传统的沟槽型MOS管,它可以减少外延层的寄生电阻,得到更低的RDS(ON)。在采用屏蔽栅极技术的Power Trench MOSFET技术之后,可以使功率MOS管具有更高的单元密度,同时在采用电荷平衡技术之寄生电阻后,可以更加有效的减少Epi电阻,从而更大程度的减小了寄生电阻的阻值,以及提高了开通与关断的特性。

在使用了飞兆半导体Power Trench结构功率MOS管之后效能是如何提高的呢?我们以一台1000W的通信电源为平台做一些产品的对照比较。在使用了飞兆半导体FDH055N15A之后,效能提升可以从最小0.2%到超过0.5%,也就是可以有最高5W的功率提升,可以从图中看出,蓝色线是使用了飞兆半导体的功率器件,红色线是竞争对手的5.9mΩ的一颗150V的相同规格的MOS管的测试曲线。

与竞争对手的Power Trench 结构功率MOS管相比,飞兆半导体屏蔽栅极技术的MOS管在同步整流的运用下有明显的优势。如图中所示,飞兆半导体的FDP036N10A与竞争对手最好的MOS管相比,在Qg值上仍然比竞争对手低10%以上。我们可以读出它的数据,飞兆半导体的FDP036N10A的Qg值是58.7,而竞争对手最好的MOS管也要达到76.2。

系统轻负载效率比较

AC-DC同步整流应用

同步整流中的驱动损耗

从左边测试曲线可以看出,在导通期间内电流从源极到漏极流过MOSFET沟道,并在死区时间流过体二极管,由于在开关瞬变期没有电压穿过同步开关,所以这里不会发生“密勒效应”,在栅-源电压上没有过渡平台。再看右边的曲线图,红色线为没有了“密勒效应”的驱动波形,可以看到它的时间相对传统MOS管的时间有着明显的缩短。

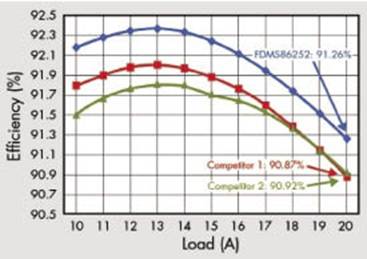

在针对隔离型和非隔离型DC-DC应用中如何提高效能,我们基于一款1/16砖的平台上做了一系列的比较试验。在采用了飞兆半导体FDMS86252与主要竞争对手产品比较,效率提升范围最小为0.4%,最大为超过1%,也就是有0.32W的功率提升,从图中可以看出,上面的曲线为采用了飞兆半导体FDMS86252的测试曲线。

众所周知低的RDS(ON)可以提高系统效能以及功率密度,这里我们针对芯片级对RDS(ON)的贡献做出分析。在比较每一串联电阻对低电压部分和高电压部分的贡献率时,可以看到,当Vg=10V、单位电流密度为200A/cm2时,外延层的电阻占的比例至关重要。在30V的VDS时,外延层的电阻只占29%,但当VDS上升到100V时,外延层的电阻将占到整个RDS(ON)的78%。所以现今在高压MOSFET上所做的大部分开发工作,都正在转向如何减少漂移区的EPI电阻。

现今如要满足行业的标准,就必须要提高设计的效率以及增加功率密度。飞兆半导体的屏蔽栅极功率MOSFET中,在5X6mm尺寸内最低RDS(ON)最大值可以做到2.5mΩ,典型值为60V的击穿电压。如右图所示,屏蔽栅极功率MOS管的击穿参数除传统的参数Cds、Cgs和Cgd之外,这里增加了CG屏蔽层以及CD屏蔽层,CG屏蔽层以及CD屏蔽层的电容作用会在后边给出解释。

<上一页123下一页> 关键字:同步整流 屏蔽 整流 RDS(ON) MOSFET 本文链接:http://www.cntronics.com/public/art/artinfo/id/80014134?page=2

飞兆半导体领先的RDS(ON)性能

基于飞兆半导体屏蔽栅极技术所提供的RDS(ON)性能,从图中可以读出,飞兆半导体屏蔽栅极技术功率MOS管测试点都在竞争对手的下边,也就是说在相同的测试条件下,飞兆半导体屏蔽栅极技术可以提供更低的RDS(ON)性能。

在选用飞兆半导体屏蔽栅极功率MOS管后,功率密度又是怎么增加的呢?我们基于AC-DC同步整流应用做一简单介绍。在选用飞兆半导体屏蔽栅极功率MOS管后,可以有效减少电压尖峰,其结果是可以使设计者选用更低额定电压的MOSFET,同时大多数应用都无需外部缓冲器。在相同测试条件下,使用飞兆半导体屏蔽栅极功率MOS管后电压尖峰可以比对手的小10%以上。

隔离型或非隔离型DC-DC的应用

同步整流中的电压尖刺损耗

在同步整流中,与器件相关的主要参数是MOS管的体二极管的柔和程度,针对于飞兆半导体屏蔽栅极功率MOS管而言,这一特性会比竞争对手更好,也就是我们定义体二级管恢复时间的TB/TA为软恢复特性,当这特性较软时,意味着同步整流中的电压尖刺可以被有效降低,其结果是可以省去缓冲器电路,或者用较低额定电压MOS管替换较高额定电压的MOS管。

屏蔽栅极技术的优势

可以带来优良的体二极管性能,而优良的体二极管性能又可以带来软反向恢复特殊和低电压尖刺,下三图是实测结果。左面是使用了飞兆半导体屏蔽栅极技术的体二极管反向恢复特性,最高毛刺电压仅有56.8V,中间图是和竞争对手最好的MOS管相比,它的方向尖峰电压仍然到63.32V。

对于隔离型或非隔离型DC-DC的应用中,在考虑到线路板空间更小,又需要增加功率密度时,我们推荐Power56的封装形式,而非D2PAK或其他封装模式。在使用了飞兆半导体屏蔽栅极功率MOS管后,可以减少开关节点的振铃现象,同时由于屏蔽栅极功率MOS管固有的电子和电容,可以实现内置的漏极到源极的缓冲电路,从而在大多数应用都无需外部缓冲电路。

与传统的Power Trench 功率MOS管相比,屏蔽栅极技术有着独特的优势。屏蔽栅极技术MOS管可以减少QGD,减少QGD带来的结果是可以拥有非常优良的开关特性及较低的振铃现象,较低的振铃现象又可以使多数情况下无需外接缓冲电路。通过比较我们可以看到,采用飞兆半导体屏蔽栅极功率MOS管后产生的振铃不到竞争对手的一半。

现在对电源系统的高能耗成本做系统分析。以服务器机架电源成本为例,预计2011年服务器数量将达到870万台,每台服务器的额定电源为4X2KW/h,即8KW/h,而每个机架有8台服务器,就是有大约100万个服务器机架,乘以8KW/h后得到额定功率为800万KW/h,以每KW/h价格0.15美元计算,最后得到成本为120万美元。对应如此高的能源成本,我们只能通过提高电源效率、提高功率密度,来节约电源的高能耗成本。

现在看看系统选用飞兆半导体的高成本效益电源之后会有什么变化。我们选用Power56技术封装的屏蔽栅极MOS管FDMS86500L,它可以使整机效率提高约1%,即每个电源每小时节电20W,每个服务器机架每年节电800W,每个服务器机架每年可以节省105美元,考虑到全部服务器机架数量为100万台,这样总体每年可以节省约11.4亿美元。这里我们可以看到,提高效率可以大幅节省成本,而提高功率密度又可以提供占位更小的解决方案,从而进一步节省成本。

总结

对于功率电源领域的发展趋势而言,更高的系统效率以及更高的功率密度已经成为各大公司及其设计人员所要达到的首要目标。根据这一系列的高要求,飞兆半导体推出了一系列的高性能的屏蔽栅极功率MOS管,可以很好的帮助设计人员解决效率以及功率密度的问题。飞兆半导体屏蔽栅极功率MOS管针对通信电源、服务器电源以及DC-DC同步整流电路,可以提高效率和功率密度,对于飞兆半导体屏蔽栅极功率MOS管的特点而言,具有低的Qg、软的体二极管的恢复特性以及极低的RDS(ON),以上特性均可以对系统的效率以及功率密度产生相当的贡献。