低压超级接面结构优化MOSFET性能

中心议题:

- MOSFET损耗问题

- 功率MOSFET结构优劣对比

- 横向/分裂闸/超级接面FOM比较

解决方案:

- 确认效益因数

- 超级接面功率MOSFET

采用超级接面结构设计的新型低压MOSFET已逐渐在市场上崭露头角,其不仅可克服现有功率MOSFET结构的缺点,亦能达到低RDS(on)、低QG和低QGD等特性,确保在兼顾晶片尺寸与功耗的前提下,提升DC-DC转换效率与功率密度。

藉由对同步交流对交流(DC-DC)转换器的功耗机制进行详细分析,可以界定必须要改进的关键金属氧化物半导体场效电晶体(MOSFET)参数,进而确保持续提升系统效率和功率密度。

分析显示,在研发功率MOSFET技术的过程中,以往常见以QG和QGD(意即RDS(on)×QG和RDS(on)×QGD)为基础的因数(FOM)已无法满足需求,若坚持采用固定因数,将可能导致技术选择无法达成最佳化。藉由此次分析的启示,工程师们已定义一套FOM以应用于新的低压功率MOSFET技术研发。由此产生的30伏特(V)技术以超级接面(Superjunction)为基础概念,是DC-DC转换器的理想选择;相较于横向和分裂闸极沟槽MOSFET等竞争技术,该技术可同时提供特定的低RDS(on)、QG、QGD、QOSS和高度闸极回跳抑制。

MOSFET损耗问题加剧 催生新功耗分析技术

多相同步降压转换器是微控制器(MCU)以及其他运算密集型积体电路(IC),如数位讯号处理器(DSP)和绘图处理器(GPU)供电的拓扑结构选择。在同步降压转换器内,两个功率MOSFET串联形成半桥结构。高处的MOSFET做为控制单结型FET;低处的MOSFET则为同步FET。

此电路拓扑演变的关键点在于2000年时,引进Pentium 4微处理器以及相关的ATX12V电源规范,其中的功率轨(即转换电压)从5伏特提高至12伏特,以达成微处理器须要快速增加电流的要求。因此而产生的工作周期变化使得功率MOSFET在性能优化方面发生重大变革,并全面采用QGD×RDS(on)和QG×RDS(on)等效益指数作为功率MOSFET的性能指标。然而,过去10年以来,特定尺寸产品中此类FOM和RDS(on)已降低约十倍,QG和QGD已不再是影响功率MOSFET功耗的主要因素。

就控制FET而言,MOSFET封装和印刷电路板(PCB)连线的寄生电感所产生的功耗可能超过由QGD产生的损耗。降低寄生电感的需求推动Power SO8封装的普及化,并使整合动力的概念于2002年产生,意即将控制和同步FET与MOSFET驱动器整合于四方形平面无接脚封装(QFN)中,此概念于2004年获英特尔(Intel)DrMOS规范采用。

为因应功率MOSFET多面性的损耗,一系列日趋复杂的运算方式和效益指数逐被提出。在功耗机制研究领域中,最被看好的技术是利用如TSuprem4和Medici等TCAD工具制作详细的行为模型,并结合详细的电路模拟(如PSpice),进而产生详细的功耗分析结果。虽然此方法可针对不同的功耗机制进行深入分析,但分析结果须转换成一套以MOSFET参数为基础的FOM,以用于新技术的研发。

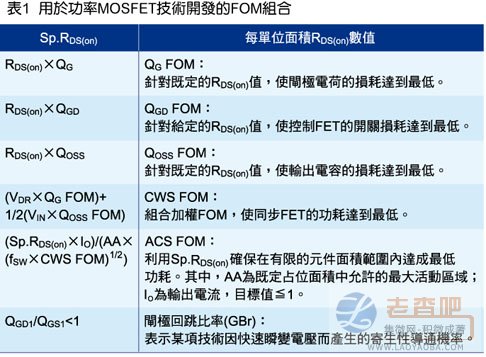

确认效益因数有助技术最佳化

为使DC-DC转换中采用的MOSFET技术达成最佳化,首先须确定对目标应用的性能造成影响的关键元件参数为何。透过功耗机制分析得出的这些参数通常为一组关键效益因数(性能指标),在确认任何效益因数的有效性为实际限值(如可用尺寸和成本)时,功耗分析所采用的假设前提相当重要。表1列出了用于新的功率MOSFET技术研发的FOM。

前三项性能指标已广泛用于评估技术的适用性,因此无须多作介绍,其仅用于告知设计工程师须尽可能减少单位面积上的RDS(on)值(即Sp.RDS(on)),以确保晶片在有限的封装尺寸内达成最高的功效。且对于特定的RDS(on),要尽量降低MOSFET电容CGS和CGD,以达成最低开关损耗。

第四个FOM为COSS,与降低输出电容有关,其重要性将逐渐增加。原因来自两方面:第一,同步FET的闸极电荷损失已大幅降低,输出电容充放电时产生的电荷损耗水准已大致相当。第二,控制FET的QGD相当微小,以致于影响电压升降时间的因素为电路电感对输出电容进行充电的时间,而非电路提供所需闸控充电的能力。在此请特别注意,表1中未列出储存电荷Qrr,并非Qrr可忽略不计,而是因为采用与上述降低Sp.RDS(on)相同的技术使其获得改善,此技术包含提高单元密度(导因于本体偏置效应)和削减漂移区块等。

设计一款高性能MOSFET须在特定的参数之间做出权衡。例如,欲改善RDS(on)×QGD,可透过加大单元间距、牺牲Sp.RDS(on)而完成,亦可透过增加一个连接源极的闸极遮罩、牺牲RDS(on)×QOSS而完成。为避免产生不符理想的元件结构,须综合这些FOM。此概念已被应用于生产综合加权同步FET(FET CWS)FOM,即综合考量闸极电荷和输出电容功耗的效应。此种FOM组合有助于对元件性能做出更精确的评估,此外,透过将转换电压和闸极驱动电压(VIN和VDR)合并后,QG和QOSS的相对重要性取决于应用方式,进而确保改善后的闸极电荷不会对输出电容产生不利影响,反之亦然。

12345下一页> 关键字:MOSFET 低压超级接面结构 本文链接:http://www.cntronics.com/public/art/artinfo/id/80014547

随着小尺寸封装晶片(如QFN3333)和多晶片产品(如DrMOS)的使用越来越为广泛,将低Sp.RDS(on)与低开关FOM相结合的确有其必要性。面积限制同步(Area Constrained sync, ACS)FET FOM组合即是透过降低RDS(on)以提高开关性能,因此须要比封装允许值更大的活动区域。请注意,该FOM不仅是一项单纯的性能指标,亦关系到该技术是否有能力达成各项性能指标在特定空间限制下所认定的潜能。因此,在进行技术比较时,须留意此点。

在理想状态下,对于CWS和ACS FOM而言,QG应在VDS=0和VGS=4.5伏特的条件下进行测量。若无法达成上述条件,可根据闸极电荷曲线,利用公式1计算QG。公式中的QG1、QG2分别为VDS1和VDS2条件下测得的闸极电荷,此两点均取自于闸极电荷曲线中QGD的部分之后。

QG=4.5V×(QG1-QG2)/(VDS1-VDS2)¨¨¨¨(公式1)

输出电荷是一般资料手册中不会提及的另一参数,但使用者可根据输出电容进行估算。当转换电压为12伏特时,假设理想的pn接面电压为0.7伏特,则QOSS可用公式2计算,其中Vm用以表示测量COSS时的电压。

QOSS=5.45×COSS(Vm)×(Vm+0.7)1/2¨¨(公式2)

最终的目标是确保MOSFET不会因为电容性电流流过闸漏电容(CGD)而导致寄生性导通,当快速VDS瞬变电流产生时,CGD会向CGS电容器充电,致使其电压超过阈值。闸极回跳比率(Gate-bounce Ratio, GBr)即用于此目标;其本质在于,当漏极电压升至输入电压电平时,如果所有流经CGD电容器的电容性电流都流入MOSFET的CGS,这时,CGS电容器的电压仍必须低于电压阈值。此一比例可利用QGD1和QGS1的值从闸极电荷曲线中轻易取得,其中,QGD1是VDS=VIN(CGD彻底充电)和VDS=VGS(CGD已放电)之间的QGD部分,QGS1为VGS=0至电压阈值之间的QGS部分。

对于控制FET方面而言,由于现代功率MOSFET的高增益特性,其电流升降时间由电路和源极电感决定,因此其余能耗则由电压升降时间决定,而这些时间则取决于QGD FOM。因此,单独为控制FET定义一个FOM组合并无实际益处。虽然CWS FOM可达成最佳化以应用于同步FET,也可用于判定COSS、CGD和CGS之间由于装置结构所产生的不利影响,但是要注意的是,由于现代元件的QGD相当低,因此,QGD不再是控制FET中功耗的主要因素。另外,由于控制FET的体积相对较小,基本上面积限制晶片尺寸的问题已不复存在,因此,采用面积受到限制的FOM亦无法增加优势。

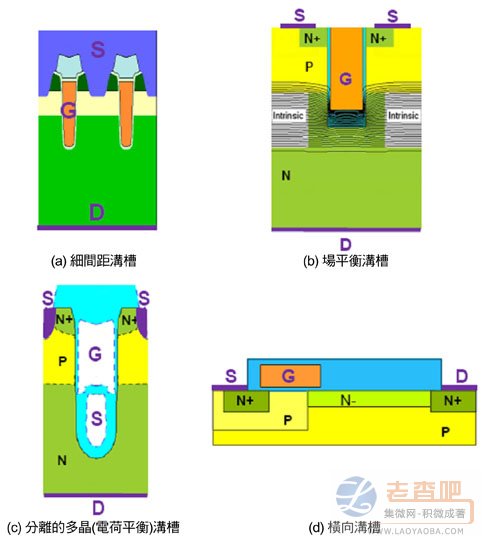

功率MOSFET结构各有优劣

图1标示出目前常用的多种功率MOSFET元件结构。图1a中所示的高密度沟槽结构采用较低的Sp.RDS(on),但QG和QGD较高,因为此两个参数与单元密度成正比。此种结构通常用于开关损耗较无重要性的应用中(如电池保护)。可透过加大单元间距、于沟槽底部加上厚氧化膜以改善此结构的开关性能。

图1 功率MOSFET结构

因单元间距加大而导致的Sp.RDS(on)上升的问题,可针对MOSFET漂移区进行设计处理以解决,如图1b所示的场平衡结构。目前最常采用的结构为分裂闸极(或电荷平衡)沟槽MOSFET,如图1c所示。此种结构闸极的正下方采用一个连接源极的遮罩电极,既可降低QGD,且透过应用降低表面电场(RESURF)原理,漂移区的电阻降至最低。当然,此结构也有其缺点,其需要较高的单元密度(因此闸极电容较高)以获得RESURF状态;另外,采用连接源极的遮罩电极将产生额外的QG和QOSS,并增加制程的复杂程度。

相反地,和沟槽结构相比,横向MOSFET结构(图1d)由于可采用RESURF技术且毋须增加单元密度,因此,可达成出色的QG和QGD FOM。但由于横向结构须要将漂移区纳入单元间距中,因此,可达成的单元密度较低,导致Sp.RDS(on)较低,进而影响到在小面积封装中为同步FET提供所需低RDS(on)的能力。

<上一页12345下一页> 关键字:MOSFET 低压超级接面结构 本文链接:http://www.cntronics.com/public/art/artinfo/id/80014547?page=2

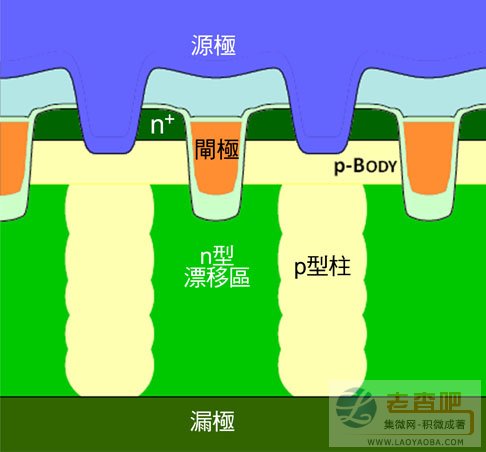

为了克服现有功率MOSFET结构的缺点,目前已经开发出一种采用超级接面概念的新型结构。低压超级接面MOSFET元件的结构如图2所示,此结构采用N-type和P-type矽区域交替形成一个多重RESURF结构,换言之,相当于将横向MOSFET结构先平行放置后,再垂直摆放,进而获得RESURF结构。这种结构克服横向结构的单元间距限制,同时,在漂移区内达成RESURF无需如同以往分裂闸结构必须依赖增加单元密度,和在每个沟槽闸下方增加CDS和CGD电容器。完成真正为DC-DC转换量身打造的元件结构。

图2 低压超级接面结构

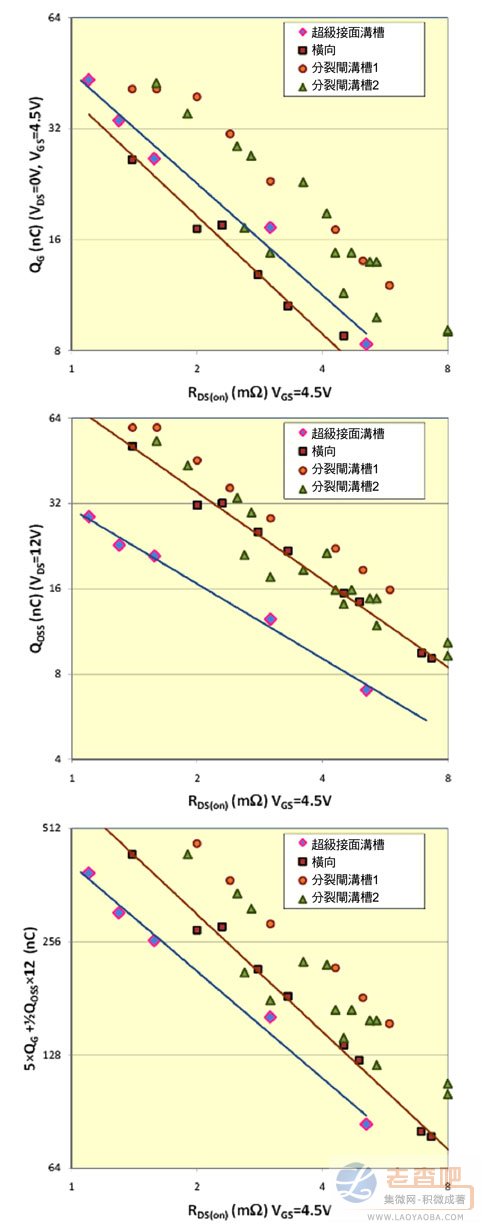

横向/分裂闸/超级接面FOM比较

采用QOSS与QG加权组合作为性能指标的优点如图3所示,其中QG、QOSS及其组合分别针对三个不同的30伏特功率MOSFET结构产生RDS(on)函数。趋势线的斜率反映不同的FOM。请注意:由于数据来自于资料手册,因此数值包含封装电阻。由图3可知,相较于超级接面和分裂闸沟槽技术,横向技术的QG更佳。由于超级接面结构在元件闸极和连接源极的漏极遮罩电极间增加了CGS,因此QG值低于分裂闸技术。

图3 针对横向/分裂闸/超级接面30V功率MOSEFT结构的QG、QOSS和QG与QOSS加权组合(CWS FOM)的比较。

<上一页12345下一页> 关键字:MOSFET 低压超级接面结构 本文链接:http://www.cntronics.com/public/art/artinfo/id/80014547?page=3

相较于采用表面漏极触点的横向元件而言,横向结构的基板与漏极连接,并在元件主体和基板间增加CDS元件,可产生较高的QOSS结构。分裂闸结构的QOSS值亦较高,因为其依赖漏源极电容的产生以遮罩闸极电极,达到低QGD和RDS(on)。而超级接面结构毋须增加额外的CDS元件,因此可达成三种结构中最低的QOSS值。

选择功率MOSFET结构的重要因素,在于考量该结构是否有助于提高元件性能。若选用横向或分裂闸结构,须考虑在低侧元件应用中,是否值得为获得低QGD和QG而牺牲QOSS性能。这些达成最佳化的结果如图3下半部分所示,QOSS和QG使用5伏特闸极驱动电压和12伏特转换电压进行组合。显然对于同步FET而言,超级接面结构因其固有的低QOSS而具备最佳的综合性能。此结果表明,仅藉由达成最佳化已不足以获得最低QG和QGD FOM。这种情况更足以证明,沟槽结构中闸极电荷已降至相当低,QG不再扮演低侧元件开关损耗的主要因素。

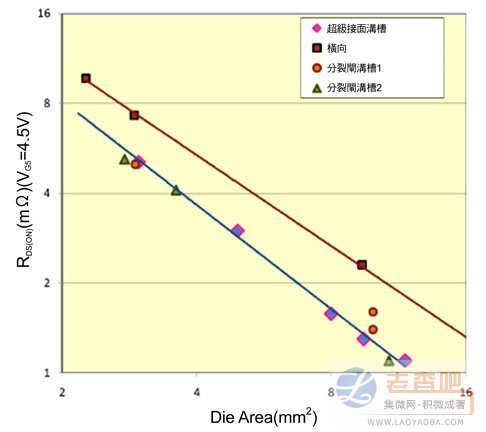

对于同步FET方面,也必须要针对Sp.RDS(on)进行权衡和取舍,因为即便在高开关频率下,导通状态下的损耗仍占大部分比例。图4显示不同技术下RDS(on)与晶片面积的关系。显而易见,横向结构需要更大的晶片才得以获得与沟槽结构相同的RDS(on)。若观察竞争对手产品的最低典型RDS(on)值(VGS=4.5伏特时),将会发现,横向技术可达成的最佳结果为1.4毫欧姆(mΩ)(CSD17312Q5)、分裂闸结构可达成1.1毫欧姆(FDMS7650),而超级接面结构可达成1.1毫欧姆(PSMN1R0-30YLC)。就Sp.RDS(on)而言,竞争产品的基准显示,当VGS=4.5伏特时,横向技术单位面积的RDS(on)值较超级接面技术和分裂闸技术的RDS(on)值高出60%。如图3所示,由于晶片的尺寸不一,上述差异并未充分反映出实际上最低的RDS(on)值。请注意,CSD17312Q5的额定闸极电压为10伏特,而沟槽技术为20伏特。如果采用相同的额定闸极电压元件进行RDS(on)比较,则其差异将更明显。

图4 针对不同的功率MOSFET结构,晶片面积与RDS(on)的关系。

封装面积缩小带来更多挑战

封装面积缩小带来另一个根本性的问题,即是否有必要牺牲Sp.RDS(on)以改善开关性能和FOM。例如,在3.3毫米(mm)×3.3毫米的QFN封装中,晶片尺寸限制在4.5平方毫米(mm2)以内。由于考量此封装限制,才设计出面积限制的同步FET FOM。为阐明Sp.RDS(on)对同步FET功耗(PL)的影响,必须考量受晶片面积公式3影响的功耗元件,其中I0为输出电流,tf为高温条件下导致MOSFET阻抗上升的温度因数,dt为MOSFET的导通时间,fSW为开关频率,VDR为闸极驱动电压,QG0为VDS=0V时VDR的闸极电荷,VIN为转换电压。在此并未提及Qrr,因为概略而言,Qrr与晶片大小无关。

PL=IO2RDS(on)×tf×dt+fSW (VDR×QG0+1/2VIN×QOSS)¨¨¨¨¨(公式3)

假设tf=1.3(即在100℃环境下运作)、导通时间为77%(相当于从12伏特转换至1.2伏特时,全负载效率的85%),上述公式可针对RDS(on)、QG0、单位面积Qoss数值以及活动区域AA改写为公式4。此外,为达成最低功耗,我们对活动区域进行区分,如公式4、5、6。

PL=IO2/AA×Sp.RDS(on)+AA×fSW (CWS FOM)/Sp.RDS(on)¨¨¨¨¨¨¨(公式4)

0=–IO2/AA2×Sp.RDS(on)+fSW (CWS FOM)/Sp.RDS(on)¨¨¨¨¨¨¨(公式5)

Sp.RDS(on)×IO=AA×(fSW(CWS FOM))1/2¨(公式6)

(Sp.RDS(on)×IO)/(AA×(fSW×CWS FOM)1/2)=1¨(公式7)

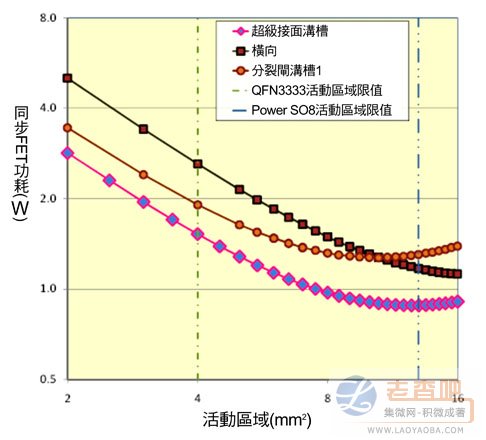

对于同步FET而言,只有在特定封装的晶片尺寸具备足够的活动区域,能够确保ACS FOM=1时,才能将功耗降至最低。图5显示当电流为25安培(A)、开关频率为500kHz时,根据公式4得出的功耗与活动区域的关系。

图5 不同的功率MOSFET结构作为同步FET时,活动区域与功耗之间的关系。开关频率为1MHz时,输出电流为25安培。电压由12伏特转换为1.2伏特,闸极驱动电压为5伏特。

<上一页12345下一页> 关键字:MOSFET 低压超级接面结构 本文链接:http://www.cntronics.com/public/art/artinfo/id/80014547?page=4

表2列出针对Power SO8和QFN3333封装的ACS FOM。对于Power SO8来说,分裂闸技术的ACS FOM最低,代表其最佳性能最易于达成。但由于CWS FOM值为最大(图3),因此,并非最佳的技术选择。值得注意的是,虽然分裂闸结构的开关FOM不如横向技术,但由于横向技术的Sp.RDS(on)较差,因此无法充分利用其开关FOM方面的优势。相反,在这三项技术中,超级接面结构同时拥有最低的Sp.Rds(on)和CWS FOM,因而能够在所需晶片面积内发挥最佳性能。当采用更小的QFN3333封装时,这些技术均无法发挥其最佳性能(三者的ACS FOM>1)。然而,图4所示的结构中,明确标示出须要进一步降低Sp.RDS(on),尽管这样做可能导致开关FOM变差,详见分裂闸技术和横向技术针对面积小于4平方毫米应用的对比。

超级接面功率MOSFET损耗低

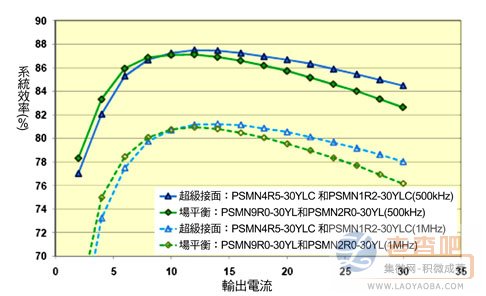

为展现超级接面功率MOSFET结构的优点,可对系统效率进行测量,并将测量结果与超级接面元件和晶片尺寸相似的场平衡结构元件做比较,工作频率为500kHz和1MHz、电压从12伏特转换为1.2伏特(图6)。当二者的晶片尺寸相同时,前者的导通状态损耗优于后者。当工作频率为500kHz和1MHz时,在30安培全负载和低负载条件下,系统效率均提高2%。超级接面晶片尺寸无论大小,均有可能出现下列情形,如重负载条件下的效率提升会牺牲轻负载效率,而轻负载条件的系统效率提升会牺牲重负载效率。采用RDS(on)较高的控制FET可能会改善效率,因为QGD降低所带来的益处大于RDS(on)升高所带来的坏处。

图6 超级接面技术与场平衡(FB)技术的效率测量结果对比,电压为12V转换至1.2V。

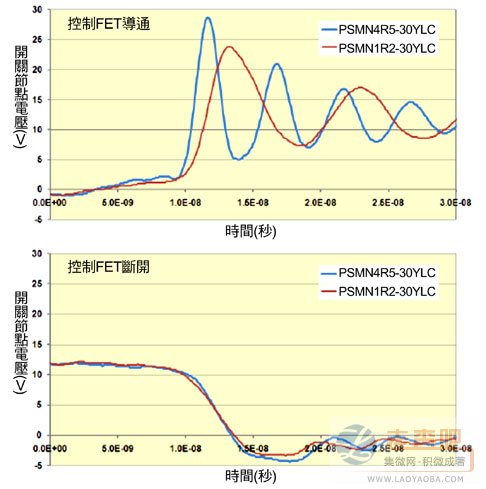

从上述中可知,控制FET的开关速度可能会受到QGD以外的其他因素限制。可从图7明显看出,低RDS(on)同步FET(PSMN1R2-30YLC)与中等RDS(on)同步FET(PSMN4R5-30YLC)的开关波形的比较。在这两个例子中,PSMN4R5-30YLC均作为控制FET。可明显地看出,开关节点(即控制FET和同步FET形成的半桥中点)的上升时间与控制FET无关。换言之,开关节点电压上升所导致的导通损耗不再受控制FET的QGD限制。

图7 PSMN4R5-30YLC和PSMN1R2-30YLC在导通和断开时的开关节点波形(即同步FET的VDS)

本例中的限制因素为电路通过寄生电感为同步FET的输出电容充电所需要的时间。结果显示使用者必须更加重视降低QOSS,而非CWS FOM隐含的值。断开操作是控制FET功耗最集中的时候,此时低RDS(on)和中等RDS(on) MOSFET的开关节点电压压降几乎是没有差别,这表示开关时间仍然受高侧元件的QGD影响。由于闸极电流比较低,且MOSFET闸极电阻具有内部分配性,控制FET的断开速度通常较慢于导通速度。因此控制FET极可能是决定元件断开时开关速度的影响因素。

在评估DC-DC转换的功率MOSFET性能时,不能仅考虑QG和QGD两个数值,因为近年来这些数值的降低,以致于必须考虑其他功耗机制。针对达成同步FET的性能最佳化,开发出两种新的FOM,分别是CWS FOM,综合了输出电荷效应(QOSS),以及考量晶片尺寸限制的ACS FOM。

新的FOM被用于分析三种不同的功率MOSFET结构。结果显示最近开发的低压超级接面结构可完美结合低RDS(on)、低QG和低QGD等特性,其性能优于横向和分裂闸等竞争产品结构。此外,随着封装尺寸缩小,ACS FOM亦显示出在功率MOSFET设计中,牺牲Sp.RDS(on)以改善开关频率并非为最佳策略。