原子层淀积技术

中心议题:

- 原子层淀积的基本原理

- 原子层淀积设备的设计

- 选择合适的金属

- 采用新型的结构

原子层淀积(ALD)技术正逐渐成为了微电子器件制造领域的必须。ALD技术于1977年首次由TuomoSuntola博士发明,他利用ZnC12和H2S来淀积应用于电致发光器件中的硫化锌薄膜。多年来,原子层淀积技术的应用范围涉及从液晶显示面板(LCDpanel)到工业涂层等多种领域,目前,该技术正被开拓到先进微电子制造工艺中,例如制备用于晶体管栅堆垛及电容器中的高k介质和金属薄膜、铜阻挡/籽晶膜、刻蚀终止层、多种间隙层和薄膜扩散阻挡层、磁头以及非挥发存储器等。

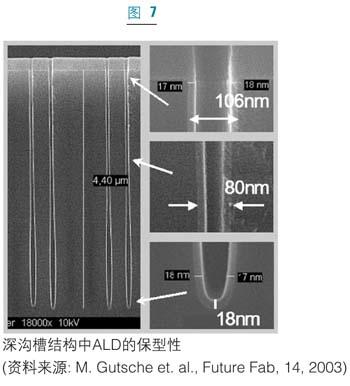

ALD相比传统的MOCVD和PVD等淀积工艺具有先天的优势。它充分利用表面饱和反应(surfacesaturationreactions),天生具备厚度控制和高度的稳定性能,对温度和反应物通量的变化不太敏感。这样得到的薄膜既具有高纯度又具有高密度,既平整又具有高度的保型性,即使对于纵宽比高达100:1的结构也可实现良好的阶梯覆盖。ALD也顺应工业界向更低的热预算发展的趋势,多数工艺都可以在400摄氏度以下进行,而传统的化学气相淀积工艺要在500摄氏度以上完成。

ALD的基本原理

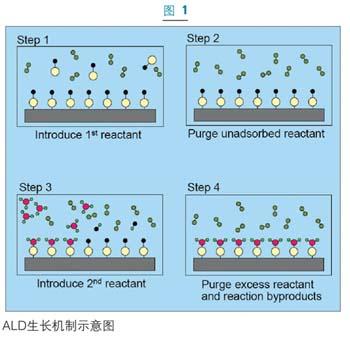

ALD的基本步骤如图一所示。这种淀积过程是在经过活性表面处理的衬底上进行的。首先将第一种反应物引入反应室使之发生化学吸附,直至衬底表面达到饱和。过剩的反应物则被从系统中抽出清除,然后将第二种反应物放入反应室,使之和衬底上被吸附的物质发生反应。剩余的反应物和反应副产品将再次通过泵抽或惰性气体清除的方法清除干净。这样就可得到目标化合物的单层饱和表面。这种ALD的循环可实现一层接一层的生长从而可以实现对淀积厚度的精确控制。

12345下一页> 关键字:原子层淀积 ALD MOCVD PVD 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006735

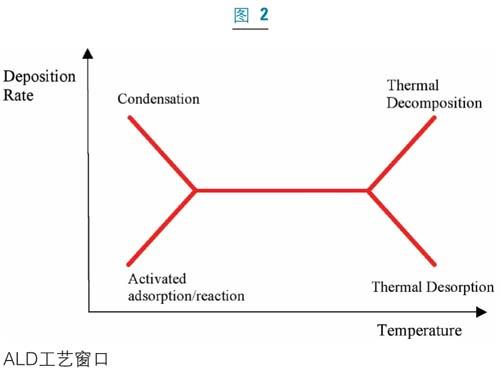

12345下一页> 关键字:原子层淀积 ALD MOCVD PVD 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006735 由于ALD是基于在交互反应过程中的自约束性生长,此工艺必须经过精细的调节来达到最合适的结果。即使原子层淀积唯一的表面反应特征降低了正常化学气相淀积对温度、压力和组分的严格要求,人们仍然需要优化ALD的参数以实现其准确的厚度控制和超级的保型性。反应室温度是用来控制表面饱和的重要参数之一,作为ALD的基础,反应室温度起着两个主要作用:提供原子层淀积反应所需的激活能量和帮助清除单原子层形成过程中的多余反应物和副产品。单原子层形成最理想的ALD温度窗口,如图2所示。ALD工艺窗口与反应物的选择、用量以及清除息息相关。为了获得完全的单层覆盖,足量的具有热稳定性的反应物,即在反应温度下不会分解的反应物,被引入到衬底上。人们往往使用过量的反应物来确保实现完全覆盖。通常采用以下几种参数来控制反应物的剂量:反应物源的温度、流量、分压以及这个反应室的压力。

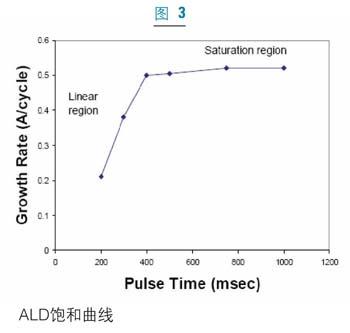

图3中的饱和曲线说明了ALD过程的自约束特性。生长率随脉冲时间呈线性增长,直到达到饱和条件。达到饱和以后,增长率为常数,且不再随脉冲时间变化而变化。但是,如果同时存在一种寄生的CVD生长成分或反应物的分解的话,增长率就会显著增加。因而,饱和曲线通常用来确定ALD的纯度。ALD生长速率介于每循环0.3埃到1.5埃间。虽然ALD的生长速率在制备很薄的膜(<200埃)时还可以接受,但在用ALD生长厚膜时,生长周期就成为挑战。

<上一页12345下一页> 关键字:原子层淀积 ALD MOCVD PVD 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006735?page=2

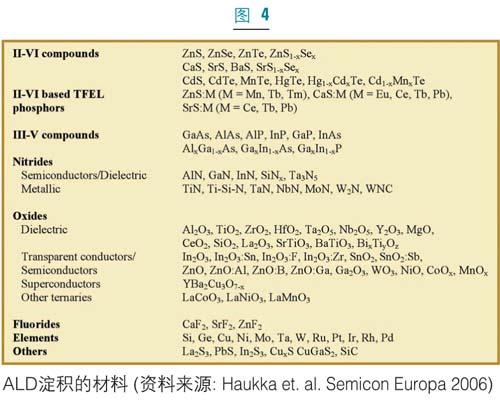

因为ALD在半导体制造的不同领域都经过评估和采用,所以选择合适的原始反应物(precursor)就变得日益重要。ALD原始反应物应当具备几个“理想”的品质,即要具有一定的挥发性和可重复的汽化率;理想情况下不应在反应温度下发生自身反应或分解;应当极易与补充反应物发生反应;应能产生可挥发的副产品;基于生长速率和成核的原因应具有最佳的配合基尺寸。为了使用方便,原始反应物最好为液体有机金属物,但是薄膜的性质和应用指标(如杂质含量、电学特性等)应该决定材料的选择。另外,对制备成本的关注也要求反应源能与传统的制备工艺在成本上更有竞争性。ALD具有很高的反应源的使用效率,这通常能平衡新反应源的高价格。随着ALD进入大规模生产,并且工业界减少对反应源的选择,对成本的顾虑将可能会随着化学品供应商规模化其生长流程而减轻。利用现有的反应源,目前人们已经可以制备多种多样的ALD薄膜(图4)。

ALD的变数

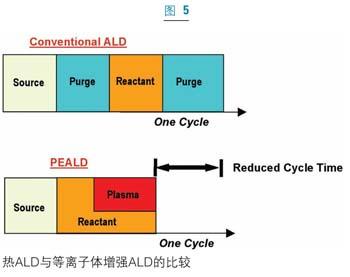

虽然ALD最初仅被视为一个纯粹的热工艺,但是对基本的原子层淀积循环的微小变更已经提出了多年。最常见的变种是等离子体增强原子层沉积工艺(PEALD)。PEALD可取消原子层淀积中的一个步骤,从而进一步缩短生产周期。PEALD过程中,在淀积温度下互不发生反应的互补反应源在同一时间被引入到反应室,然后反应源关闭并净化反应室,接着施加一个直接的等离子脉冲,这个等离子体环境产生高活性自由基并与吸附于衬底的反应物反应。关闭等离子可迅速清除活性自由基源,反应室中一直流过的清洁气体将清除过剩自由基和反应副产物(图5)。除了较高的生长速度和较短的周期时间,PEALD薄膜表现出比传统的原子层淀积薄膜更高的密度和更高的击穿电压。该技术已经在多个应用中取得了发展,如DRAM、MIM和eDRAM电介质薄膜。不过在一些关键的薄膜应用中,如高功率栅介质,等离子损伤以及界面氧化的顾虑阻碍了PEALD技术的广泛应用。

硬件设计

ALD设备的设计通常可分为热壁反应室和冷壁反应室两大类。热壁反应室将整个反应室维持或接近于淀积温度,热壁反应室的主要优势是在反应室侧壁上所淀积的也都是高品质的ALD薄膜,热壁反应室设备往往能阻止薄膜的早期剥离,由于从加热的侧壁脱附的反应源流量较高,从而加速了对反应空间的清洁。冷壁反应室通常只将衬底加热到淀积温度,其它反应室组件却维持在较低的温度,这将有利于传送在淀积温度可能分解的反应物,但风险是易受长时间净化的影响,冷壁表面的反应源脱附速率的降低导致了更大的化学气相淀积成分。随着反应室内淀积薄膜的积累,上述问题会进一步恶化。

不同配置的ALD设备可用于半导体制造的不同工艺中。ALD反应室可以是单晶圆设备、小批量晶圆(<25晶圆负载)设备、或大批量晶圆(50-100晶圆负载)系统。单晶圆设备可以实现对工艺极好地控制,而多晶圆系统能极大地提升生产能力。应用对薄膜的要求决定如何选择合适的设备装置。此外,一些ALD薄膜很难均匀地在大批量晶圆系统中淀积,这就必须使用单晶圆或小批量晶圆工艺设备。<上一页12345下一页> 关键字:原子层淀积 ALD MOCVD PVD 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006735?page=3

应用

自从CMOS晶体管发明以来,二氧化硅和后来的氮氧硅已经成为完美的栅介质材料,使得栅介质厚度从1000埃减小到大约10个埃。这使得集成电路的晶体管数量大约每24个月翻一番(摩尔定律),目前量产器件的尺寸已缩小到65纳米技术节点。由于量子力学隧穿机理,电子很容易通过非常薄的栅氧化层,进一步减小二氧化硅会造成额外的功率损耗问题。在45nm及以下工艺,较厚的高k电介质材料替代了二氧化硅或氮氧硅栅介质以减少漏电流。高K栅介质的等效氧化层厚度的表达式为:

EOT=(kSiO2/kHK)/tox

Ksio2为二氧化硅的介电常数,Khk为高K介质材料介电常数,tox为高K介质材料的物理厚度。采用高k材料,能够淀积较厚薄膜,同时保持结栅介质EOT的缩放比例。栅氧化层高K材料必须被淀积以取代在过去几十年中的关键栅氧化工艺方法-热氧化工艺方法。这在世界半导体产业是一个巨大的变化,因为一种淀积工艺方法现在必须达到氧化炉中得到的栅氧介质的均匀性和缺陷特性。业界的领先企业在45纳米技术节点正引入基于铪(Hf)的高k栅介质化合物,其它公司有望32纳米节点采用高k栅方案。

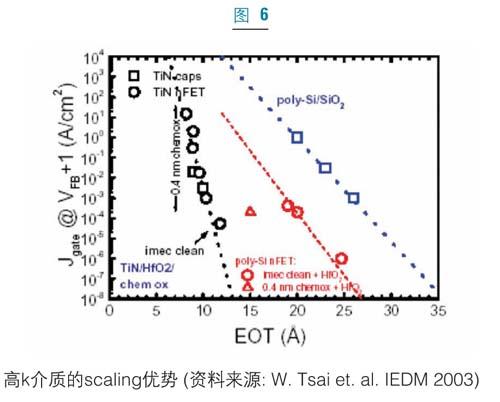

当高k材料替代二氧化硅材料后,金属栅必须取代传统的多晶硅栅以充分实现电学优势。由于费米能级钉扎效应,多晶硅耗尽和化学不稳定性,多晶硅栅电极已被发现与高k栅介质不兼容。图6显示了二氧化硅(SiO2)和二氧化铪(HfO2)栅介质的栅级漏电流比较。在相同的等效氧化层厚度(EOT)下,HfO2/TiN栅堆的栅漏电流要比传统的SiO2/Poly-Si栅堆的栅漏电流小好几个数量级。

然而,金属栅集成到栅工艺的模块中是极其复杂的。选择合适的金属是非常关键的,因为作为电极其功函数必须能够调校到CMOS器件的合适工作范围之内。这将可能引入双金属栅方法:即为nMOS和pMOS晶体管提供不同的金属栅。后续处理工艺也能影响到金属电极的功函数,从而导致电学性能的偏移,如阈值电压等。高温处理(约1000℃),如源/漏极的掺杂激活退火,可以导致金属电极的功函数移动和高k介质材料的晶化。现在已对可以减轻这些效应的一些技术进行了研究,包括在栅介质和金属栅之间采用薄覆盖(cap)层以帮助调节功函数,并添加氧化锆(ZrO2)到二氧化铪(HfO2)薄膜中以增加在高温处理过程中高k栅介质的稳定性。

<上一页12345下一页> 关键字:原子层淀积 ALD MOCVD PVD 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006735?page=4

<上一页12345下一页> 关键字:原子层淀积 ALD MOCVD PVD 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006735?page=4 半导体制造中首次大量采用ALD是在动态存储器(DRAM)工艺中。动态存储器的设计尺寸越来越小是为了提高电容密度和减小存储器每一比特的成本。动态存储器设计中要求高纵宽比的沟槽结构,原子层淀积具有这种功能,并能淀积高质量的膜层。用ALD淀积的高k介质能进一步减小EOT,自2000年开始,ALD三氧化二铝(Al2O3)就应用于动态存储器(DRAM)制造中。

最近,Al2O3/HfO2以及Al2O3/ZrO2结构也引起了人们的关注。PEALD也已经用于eDRAM中。电容满足所有的要求,即等效氧化层厚度要小于8埃,125摄氏度时漏电流要小于1fA/cell,工作电压为1伏时寿命要大于十年。图7为典型的ALD薄膜在深槽结构的保角性和动态存储器生产中的半球形硅晶结构,金属ALD薄膜,例如氮化钛(TiN)也广泛应用于动态存储器制造中的电容电极。

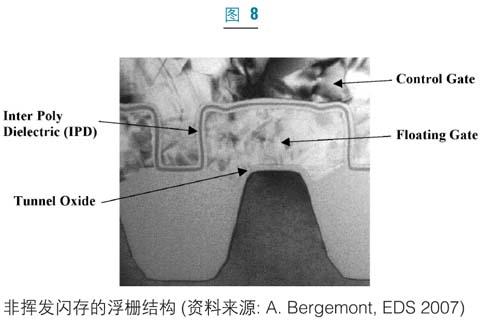

在非挥发性存储器的应用中,人们也开始研究ALD在介质和金属淀积中的应用。闪存技术主要由浮栅(floatinggate)技术主导(图8)。高k电介质目前正被研究作为二氧化硅(SiO2)和氮化硅(Si3N4)栅介质的替代品,以改善浮栅和控制栅之间的电容耦合率。到2010年,浮栅技术可望被一些技术所取代,例如电荷捕获存储器(TANOS,NROM),相变存储器(PCM)、铁电记忆体(存储器),三维堆叠式存储器也正在研究中。ALD已被用作这些技术的阻挡层和扩散阻挡层。

在半导体产业之外,ALD的重要性也今非昔比。ALD氧化铝在制备薄膜磁头(THMH)制造中已经使用了许多年。THMH复杂结构,包括多层薄金属和介质薄膜。ALD薄膜层被用作磁头结构中的带隙介质层和硅片级处理完成后的压缩层。

ALD技术的独特性决定了其在半导体工业中的运用前景十分广泛。器件尺寸的缩小导致的介质薄膜厚度的减小已超出了其物理和电学极限,同时高纵宽比在器件结构中随处可见。由于传统的淀积技术很难满足需求,ALD技术已充分显示了其优势,为器件尺寸的继续微缩提供了更加广阔的空间。

<上一页12345 关键字:原子层淀积 ALD MOCVD PVD 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006735?page=5