准谐振反激式电源设计之探讨

中心议题:

- 对于准谐振反激式电源设计的探讨

- 硬开关转换器中的寄生电容产生EMI

- 寄生电容被充电到最小电压,导通的电流尖峰将最小

- 导通电流尖峰的减小等都会减少EMI

成本和高可靠性是离线电源设计中两个最重要的目标。准谐振 (Quasi resonant) 设计为设计人员提供了可行的方法,以实现这两个目标。准谐振技术降低了MOSFET的开关损耗,从而提高可靠性。此外,更软的开关改善了电源的EMI特性,允许设计人员减少使用滤波器的数目,因而降低成本。本文将描述准谐振架构背后的理论及其实施,并说明这类反激式电源的使用价值。

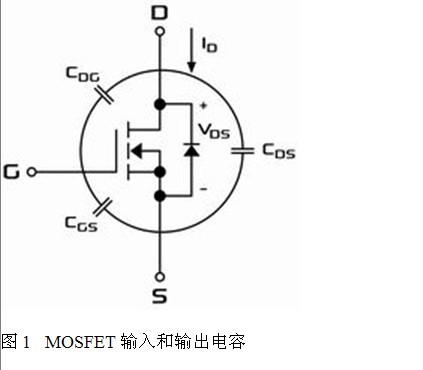

基本知识“准”(quasi)是指有点或部分的意思。在实现准谐振的设计中,现有的L-C 储能电路正战略性地用于PWM电源中。结果是L-C 储能电路的谐振效应能够“软化”开关器件的转换。这种更软的转换将降低开关损耗及与硬开关转换器相关的EMI。由于谐振电路仅在相当于其它传统方波转换器的开关转换瞬间才起作用,故而有 “准谐振”之名。要理解这种设计的拓扑结构,必须了解MOSFET和变压器的寄生特性。MOSFET包含若干个寄生电容,主要从器件的物理结构产生。它们可以数学方式简化为MOSFET输入电容CISS和MOSFET输出电容COSS,这里CISS = CGS + CDGCOSS = CDS + CDG在硬开关转换器中,输出电容COSS是开关损耗的主要来源。

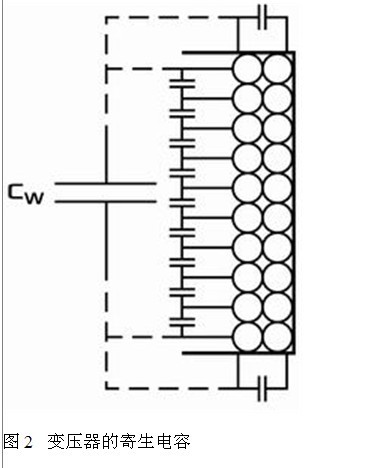

这些电容包括绕组间电容和层间电容,它们可以一起转型为单一的电容CW,也是硬开关转换器开关损耗的主要来源。

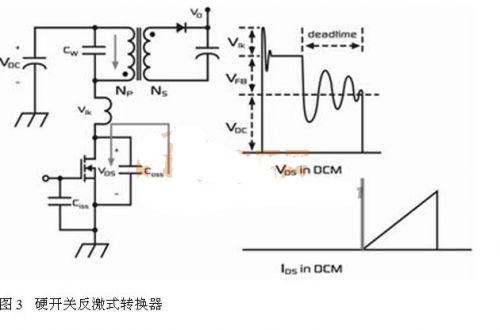

硬开关转换器中的寄生电容

图3示出传统硬开关反激式转换器。在这种传统的间断模式反激式转换器 (DCM) 的停滞时间期间,寄生电容将与VDC周围的主要电感发生振荡。寄生电容上的电压会随振荡而变化,但始终具有相当大的数值。当下一个时钟周期的MOSFET 导通时间开始时,寄生电容 (COSS和CW) 会通过MOSFET放电,产生很大的电流尖峰。由于这个电流出现时MOSFET存在一个很大的电压,该电流尖峰因此会做成开关损耗。此外,电流尖峰含有大量的谐波含量,从而产生EMI。12下一页> 关键字:准谐振 开关转换器 反激式电源 漏源电压 本文链接:http://www.cntronics.com/public/art/artinfo/id/80011879

准谐振反激式设计的实现

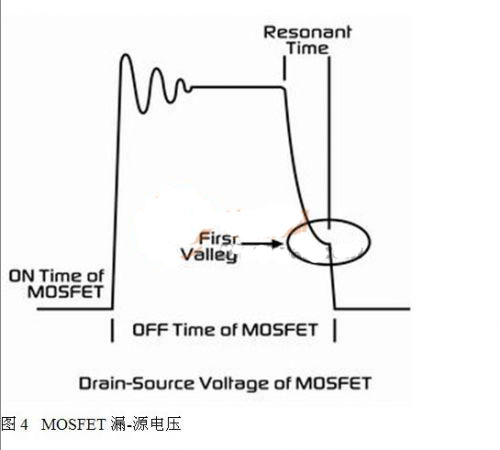

如果不用固定的时钟来初始化导通时间,而利用检测电路来有效地“感测”MOSFET (VDS) 漏源电压的第一个最小值或谷值,并仅在这时启动MOSFET导通时间,情况又会如何?结果会是由于寄生电容被充电到最小电压,导通的电流尖峰将会最小化。这情况常被称为谷值开关 (Valley Switching) 或准谐振开关。在某些条件下,设计人员甚至可能获得零电压开关 (ZVS),即当MOSFET被激活时没有漏源电压。在这情况下,由于寄生电容没有充电,因此电流尖峰不会出现。这种电源本身是由线路/荷载条件决定的可变频率系统。换言之,调节是通过改变电源的工作频率来进行,不管当时负载或线路电压是多少,MOSFET始终保持在谷底的时候导通。这类型的工作介于连续 (CCM) 和间断条件模式 (DCM) 之间。因此,以这种模式工作的转换器被称作在边界条件模式 (BCM) 下工作。

准谐振或谷值开关的优势

在反激式电源设计中采用准谐振或谷值开关方案有着若干优势。降低导通损耗这种设计为设计人员提供了较低的导通损耗。由于FET转换具有最小的漏源电压,在某些情况下甚至为零,故可以减小甚至消除导通电流尖峰。这减轻了MOSFET的压力以及电源的EMI。降低关断损耗准谐振也意味着更小的关断损耗。由于规定FET会在谷值处进行转换,在某些情况下,可能会增加额外的漏源电容,以减低漏源电压的上升速度。较慢的漏源电压上升时间会减少FET关断时漏级电流和漏源电压之间的电压/电流交迭,使到MOSFET的功耗更少,从而降低其温度及增强其可靠性。

减少EMI

导通电流尖峰的减小或消除以及较慢的漏源电压上升速度都会减少EMI。一般而言,这就允许减少EMI滤波器的使用数量,从而降低电源成本。

结语

降低成本和增加可靠性永远都是电源设计人员的目标。利用准谐振技术可以协助设计人员实现这些目标。准谐振或谷底开关能减轻MOSFET的压力,从而提高其可靠性。利用准谐振技术,由于波形的谐波含量降低,电源的EMI因此得以减少。<上一页12 关键字:准谐振 开关转换器 反激式电源 漏源电压 本文链接:http://www.cntronics.com/public/art/artinfo/id/80011879?page=2