SRAM特点及工作原理

中心议题:

- SRAM的基本简介

- SRAM的主要规格与特点

- SRAM的结构与工作原理

- CPU与主存之间的高速缓存

- CPU内部的L1/L2或外部的L2高速缓存

- CPU外部扩充用的COAST高速缓存

SRAM是英文StaticRAM的缩写,它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据.

基本简介

SRAM不需要刷新电路即能保存它内部存储的数据。而DRAM(DynamicRandomAccessMemory)每隔一段时间,要刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,且功耗较大。所以在主板上SRAM存储器要占用一部分面积。

主要规格

一种是置于CPU与主存间的高速缓存,它有两种规格:一种是固定在主板上的高速缓存(CacheMemory);另一种是插在卡槽上的COAST(CacheOnAStick)扩充用的高速缓存,另外在CMOS芯片1468l8的电路里,它的内部也有较小容量的128字节SRAM,存储我们所设置的配置数据。还有为了加速CPU内部数据的传送,自80486CPU起,在CPU的内部也设计有高速缓存,故在PentiumCPU就有所谓的L1Cache(一级高速缓存)和L2Cache(二级高速缓存)的名词,一般L1Cache是内建在CPU的内部,L2Cache是设计在CPU的外部,但是PentiumPro把L1和L2Cache同时设计在CPU的内部,故PentiumPro的体积较大。最新的PentiumII又把L2Cache移至CPU内核之外的黑盒子里。SRAM显然速度快,不需要刷新的操作,但是也有另外的缺点,就是价格高,体积大,所以在主板上还不能作为用量较大的主存。

基本特点

现将它的特点归纳如下:

◎优点,速度快,不必配合内存刷新电路,可提高整体的工作效率。

◎缺点,集成度低,功耗较大,相同的容量体积较大,而且价格较高,少量用于关键性系统以提高效率。

◎SRAM使用的系统:

○CPU与主存之间的高速缓存。

○CPU内部的L1/L2或外部的L2高速缓存。

○CPU外部扩充用的COAST高速缓存。

○CMOS146818芯片(RT&CMOSSRAM)。

主要用途

SRAM主要用于二级高速缓存(Level2Cache)。它利用晶体管来存储数据。与DRAM相比,SRAM的速度快,但在相同面积中SRAM的容量要比其他类型的内存小。

SRAMSRAM的速度快但昂贵,一般用小容量的SRAM作为更高速CPU和较低速DRAM之间的缓存(cache).SRAM也有许多种,如AsyncSRAM(AsynchronousSRAM,异步SRAM)、SyncSRAM(SynchronousSRAM,同步SRAM)、PBSRAM(PipelinedBurstSRAM,流水式突发SRAM),还有INTEL没有公布细节的CSRAM等。12下一页> 关键字:SRAM 存储器 高速缓存 本文链接:http://www.cntronics.com/public/art/artinfo/id/80007536

基本的SRAM的架构如图1所示,SRAM一般可分为五大部分:存储单元阵列(corecellsarray),行/列地址译码器(decode),灵敏放大器(SenseAmplifier),控制电路(controlcircuit),缓冲/驱动电路(FFIO)。SRAM是静态存储方式,以双稳态电路作为存储单元,SRAM不象DRAM一样需要不断刷新,而且工作速度较快,但由于存储单元器件较多,集成度不太高,功耗也较大。

工作原理

图2六管单元电路图SRAM的工作原理:

假设准备往图2的6T存储单元写入“1”,先将某一组地址值输入到行、列译码器中,选中特定的单元,然后使写使能信号WE有效,将要写入的数据“1”通过写入电路变成“1”和“0”后分别加到选中单元的两条位线BL,BLB上,此时选中单元的WL=1,晶体管N0,N5打开,把BL,BLB上的信号分别送到Q,QB点,从而使Q=1,QB=0,这样数据“1”就被锁存在晶体管P2,P3,N3,N4构成的锁存器中。写入数据“0”的过程类似。

SRAM的读过程以读“1”为例,通过译码器选中某列位线对BL,BLB进行预充电到电源电压VDD,预充电结束后,再通过行译码器选中某行,则某一存储单元被选中,由于其中存放的是“1”,则WL=1、Q=1、QB=0。晶体管N4、N5导通,有电流经N4、N5到地,从而使BLB电位下降,BL、BLB间电位产生电压差,当电压差达到一定值后打开灵敏度放大器,对电压进行放大,再送到输出电路,读出数据。

结构原理

SRAM(StaticRAM),即静态RAM.它也由晶体管组成。接通代表1,断开表示0,并且状态会保持到接收了一个改变信号为止。这些晶体管不需要刷新,但停机或断电时,它们同DRAM一样,会丢掉信息。SRAM的速度非常快,通常能以20ns或更快的速度工作。一个DRAM存储单元仅需一个晶体管和一个小电容.而每个SRAM单元需要四到六个晶体管和其他零件。所以,除了价格较贵外,SRAM芯片在外形上也较大,与DRAM相比要占用更多的空间。由于外形和电气上的差别,SRAM和DRAM是不能互换的。

SRAM的高速和静态特性使它们通常被用来作为Cache存储器。计算机的主板上都有Cache插座。

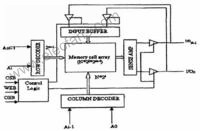

SRAM下图所示的是一个SRAM的结构框图。由上图看出SRAM一般由五大部分组成,即存储单元阵列、地址译码器(包括行译码器和列译码器)、灵敏放火器、控制电路和缓冲/驱动电路。在图中,A0-Am-1为地址输入端,CSB.WEB和OEB为控制端,控制读写操作,为低电平有效,1100-11ON-1为数据输入输出端。存储阵列中的每个存储单元都与其它单元在行和列上共享电学连接,其中水平方向的连线称为“字线”,而垂直方向的数据流入和流出存储单元的连线称为“位线”。通过输入的地址可选择特定的字线和位线,字线和位线的交叉处就是被选中的存储单元,每一个存储单元都是按这种方法被唯一选中,然后再对其进行读写操作。有的存储器设计成多位数据如4位或8位等同时输入和输出,这样的话,就会同时有4个或8个存储单元按上述方法被选中进行读写操作。

在SRAM中,排成矩阵形式的存储单元阵列的周围是译码器和与外部信号的接口电路。存储单元阵列通常采用正方形或矩阵的形式,以减少整个芯片面积并有利于数据的存取。以一个存储容量为4K位的SRAM为例,共需12条地址线来保证每一个存储单元都能被选中(212=-4096)。如果存储单元阵列被排列成只包含一列的长条形,则需要一个12/4K位的译码器,但如果排列成包含64行和64列的正方形,这时则只需一个6/64位的行译码器和一个6/64位的列译码器,行、列译码器可分别排列在存储单元阵列的两边,64行和64列共有4096个交叉点,每一个点就对应一个存储位。

因此,将存储单元排列成正方形比排列成一列的长条形要大大地减少整个芯片地面积。存储单元排列成长条形除了形状奇异和面积大以外,还有一个缺点,那就是排在列的上部的存储单元与数据输入/输出端的连线就会变得很长,特别是对于容量比较大得存储器来说,情况就更为严重,而连线的延迟至少是与它的长度成线性关系,连线越长,线上的延迟就越大,所以就会导致读写速度的降低和不同存储单元连线延迟的不一致性,这些都是在设计中需要避免的。

<上一页12 关键字:SRAM 存储器 高速缓存 本文链接:http://www.cntronics.com/public/art/artinfo/id/80007536?page=2