DDR测试系列之一——力科DDR2测试解决方案

中心议题:DDR2总线,DDR2相关测试以及力科的DDR2全方位测试解决方案

DDR2简介

从1998年的PC100到今天的DDR3,内存技术同CPU前端总线一道经历着速度的提升及带宽的扩展。虽然DDR3在当今已经量产与使用,DDR2在实际上还担任着内存业界应用最广泛最成熟的中流砥柱的角色。

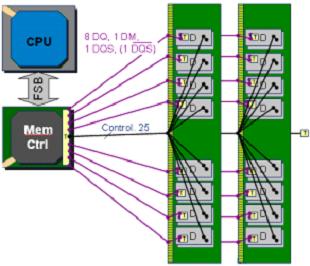

DDR2在DDR的基础上将芯片接口时钟频率提高一倍并将工作电压从2.5V降低至1.8V,从而使其能在相对更低的功耗下获得更高的传输速率。一般情况下,DDR2的输入时钟频率覆盖200/266/333/400/533MHz,传输比特率覆盖400/533/667/800/1066Mb/s/pin。相对于DDR,由于速度的提升,DDR2在主板设计要求上也有所变化。内存控制器每Channel可级联的DIMM数从DDR时期的4到8条减少至2到3条,数据线(DQ)上的终端电阻从主板上的分立电阻搬移到了DRAM芯片内部(ODT),数据同步信号(DQS)由单端信号变为单端或差分可选信号。DDR2主板系统架构如右图所示。

图1 DDR2主板系统架构

DDR2总线与工作流程

以通用计算机主板上的DDR2总线为例,DDR2信号线可以分为数据、命令、时钟3部分。其中数据线部分主要完成数据传输工作,包括数据线DQ0-63、Data Mask线DM0-7、数据同步线DQS/DQS# (数据同步线可选单端或差分,通过设定内存芯片内部寄存器EMR[1]的A10位进行选择);命令线部分包括地址线A0-14、Bank选择线BS0-2、行地址选择RAS#、列选择CAS#、写使能WE#、片选CS#、时钟使能CKE及芯片内部终端电阻使能ODT组成,主要完成寻址、组成各种控制命令及内存初始化工作;差分时钟信号线CK/CK#为整个内存芯片工作提供时钟。

所有的信号线中,除了数据线DQ与数据同步线DQS/DQS#为双向信号线外,其余所有信号线均为单向信号线,只能由内存控制器发出信号。

对于电源和地线,内存颗粒上有一个参考电压输入和三组1.8V电源与地线,分别为芯片上的数据端口,锁相环和芯片电路供电。

对于DDR2内存的工作流程可以非常粗略的概括如下:内存系统上电后由内存控制器对内存芯片进行初始化,主要是配置芯片的工作模式寄存器(MRS/EMRS),从而将内存芯片配置为某种特定的工作模式。初始化完成之后内存芯片便进入Idle模式,此时便可接收控制命令将芯片内部某Bank激活,该Bank所在的地址代表了后面读写某个具体内存地址时的行地址。

Bank激活之后便可接收读/写命令及对应的列地址从而进行相应的读写操作了。

右图为DDR2 SDRAM简化的工作状态图,从图上可以看出内存芯片具体的工作过程实际上是非常复杂的,中间包括了芯片各种状态的转换、易失存储单元的数据刷新以及读写操作的中断等等。也正是由于DDR2芯片工作的这种复杂性,加之DDR2测试项目指标众多,导致了我们在对DDR2总线进行手工测试时异常复杂与繁琐,致使手工对DDR2信号进行较全面的测试几乎成了不可能完成的任务。

力科推出的QPHY-DDR2一致性测试软件包使这个复杂的问题迎刃而解,它可以自动测试JEDEC组织规定的所有DDR2一致性测试项目并自动生成测试报告,从而极大的提高DDR2测试的精确性与效率。

图二 DDR2 SDRAM简化的工作状态图

123下一页> 关键字:DDR2简介 DDR2 DDR2测试 DDR3 时钟测试 探头选型 测试工作坊 本文链接:http://www.cntronics.com/public/art/artinfo/id/80003793

DDR2测试项目

DDR2信号测试项目可主要分为时钟测试,电气性能测试及时序测试三个部分。

一)时钟测试

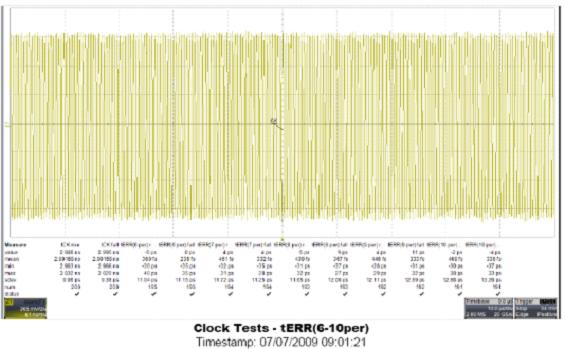

时钟测试部分主要测试差分时钟信号线CK/CK#的各方面参数,包括绝对及平均时钟周期、绝对及平均高/低脉宽、占空比抖动、周期抖动、Cycle to Cycle抖动以及连续n周期累积误差tERR(n per)。其中连续n周期累积误差tERR(n per)为统计测量时钟信号连续n个周期时间与n倍平均时钟周期时间的差值,其具体计算公式如下:

JEDEC标准要求测量n分别为2、3、4、5、6-10、11-15时tERR(n per)的最大及最小值。对于这样的要求,如果要用手工测量将是非常耗时且低效率的。力科QPHY-DDR2软件包的时钟测量部分支持上述所有参数的自动测量,仅需使用一根差分探头将时钟信号接入示波器即可完成所有的测量工作,测量后的所有参数结果及对应波形将列在自动生成的测试报告中并与JEDEC标准中门限值进行比较。如下图为使用QPHY-DDR2测量tERR(6-10 per)时的部分结果与对应波形。

图三 力科QPHY-DDR2测量tERR(6-10 per)的部分结果与对应波形

二)电气性能测试

DDR2电气性能测试部分主要测量各信号的直/交流逻辑高/低电平、信号过冲/下冲幅度及范围、差分信号DQS及Clock输入电压及交叉点电压、DQ及DQS输出信号上升/下降沿斜率(SoutR、SoutF)最大/最小值、DQ,DQS及Clock输入信号上升/下降沿斜率(SlewR、SlewF)最小值等等。

对斜率测量时,由于DQ及DQS信号为双向信号线,需要首先对数据线上的信号进行读写分离,之后才能分别测量写操作时的输入斜率及读操作时的输出斜率。实际上,对于时序测量部分的很多指标包括输入/输出前导时间及建立/保持时间等进行测量时,同样需要首先对数据线上的信号进行读写分离。

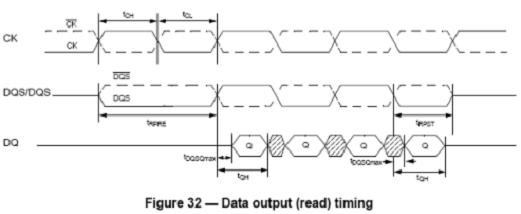

下图为JEDEC标准中所绘制的一个简单的读操作波形。从图中我们可以看出,DQS与DQ信号基本上是边沿对齐的。同时,在DQ线上出现数据的前一个时钟周期DQS信号会被置低作为前导信号,之后DQ会随着DQS的跳变而依次送出4或8个连续的Burst数据。

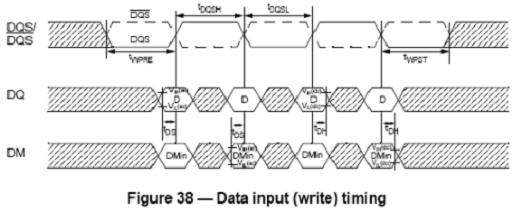

下图为JEDEC标准中所绘制的一个简单的写操作波形。对比上图的读操作波形,我们可以看出两者时序上的区别主要在于,DDR2写操作时DQ或DM的数据中心与DQS信号边沿对齐,DQS前导信号的低脉冲长度明显减小,大约为半个时钟周期或以下。

总体而言,可以从以下几个方面进行DDR2读写分离:

1.读操作DQS跳变点与DQ跳变沿对齐,写操作DQS跳变点对齐DQ中心。

2.读操作DQS前导信号为大约一个时钟周期,写操作DQS前导信号大约为半个时钟周期或以下。

3.比较波形峰峰值。一般情况下,在内存控制器端测量时,写操作峰峰值高;在内存芯片端测量时读操作峰峰值高。

对DDR2信号进行精确的读写分离是比较困难的,原因在于读写时序本身比较复杂,中间涉及到内存芯片各工作状态之间的转换、读写Burst、连读连写及Burst中断等等各种可能因素。依靠手工分离DDR2读写信号不但费时且精度不高,同时由于读写信号分离是DDR2很多参数测量的前提,能否正确高效的进行读写分离便成为了DDR2测量的一个关键点。力科QPHY-DDR2软件可以自动对输入示波器的大量DDR2数据及时钟信号进行分析,精确地从双向数据线中分离出读写信号并进行后续的相关参数测试,从而保证了DDR2一致性测试的精确性与高效率。

<上一页123下一页> 关键字:DDR2简介 DDR2 DDR2测试 DDR3 时钟测试 探头选型 测试工作坊 本文链接:http://www.cntronics.com/public/art/artinfo/id/80003793?page=2

三)时序测试

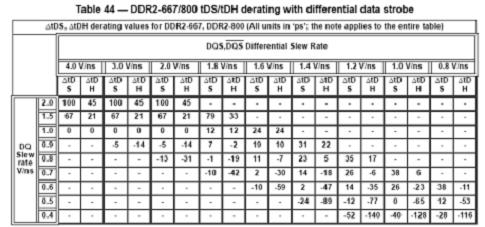

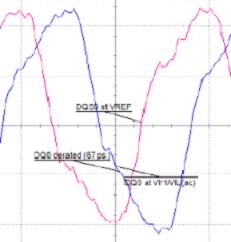

时序测试部分主要对DDR2数据、时钟及控制线上各种时序进行测量,包括数据输入建立/保持时间、数据输出保持时间、数据读/写时DQS前导/后续时间、时钟半周期宽度、DQS输入高/低脉冲宽度等等二十余项参数。其中,在对数据输入建立/保持时间(tDS、tDH)进行测量时,JEDEC标准规定需要根据写数据时的DQ及DQS信号斜率对测得的建立保持时间进行修正。下表为JEDEC标准中对应DDR2 667/800的输入建立/保持时间修正参数表。例如,写操作时当DQ测得的斜率为1.5V/ns,DQS斜率为3.0V/ns时,测得的DQ – DQS建立/保持时间需要加上67ps的修正值之后方能与标准中规定的最小建立/保持时间相比较。

为了在上表中查到对应的修正值,需要首先得出相应信号的斜率。JEDEC标准规定了两种斜率计算方法,即直连斜率norminal slew rate和切线斜率tangent slew rate,分别在不同数据波形时采纳。两种斜率计算方法如下图所示。

图四 直连斜率norminal slew rate 图五 切线斜率tangent slew rate

当信号波形在阴影标定区域内一直早于直连斜率这根蓝色直线时使用直连斜率计算并查找建立/保持时间修正值,当信号波形在阴影标定区域内有任何一点落在直连斜率线之后时则需使用图五所示的切线斜率计算和查找建立/保持时间修正值。

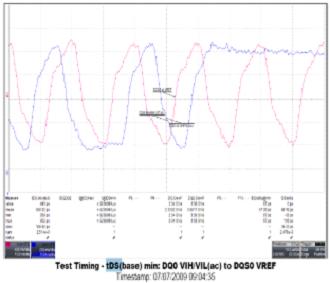

由上可知,对DDR2数据输入建立/保持时间(tDS、tDH)测量是一件比较繁琐且费时的过程,而应用力科QPHY-DDR2软件测量时,以上的所有操作均由软件自动完成,这些复杂的流程对操作者完全透明,在大大减轻DDR2测试复杂度的同时提高了测试结果的准确性。如下图所示,在tDS 测试时QPHY-DDR2自动找出了对应的67ps建立时间修正值。

力科DDR2一致性测试解决方案QPHY-DDR2

力科QPHY-DDR2测试解决方案可以对DDR2总线进行全方位的自动化测试,支持所有标准速率的DDR2内存系统(400/533/667/800/1066M)及用户自定义的其他DDR2工作速度,可对JEDEC组织及Intel规定的所有DDR2测试项目进行测试。

QPHY-DDR2的操作非常简单,如右图所示,它使用友好的图形化界面引导用户从探头与被测系统连接开始一步步完成DDR2的所有测试。目前为止,力科DDR软件包是能支持的测试项目最多的。

图六 QPHY-DDR2 图形化用户界面

对于DDR2众多的测试指标,用户可以在QPHY-DDR2中任意选择测量DDR2中的某一项或多项指标(如下图7所示),也可以选择一次测量所有规定的测试项目。测试完成后,所有的测试结果及相应的波形均被列入到自动生成的测试报告中(如下图8所示),用户可以一目了然地了解被测DDR2系统的各指标性能。

图7 测试参数选择界面 图8 DDR2测试报告首页

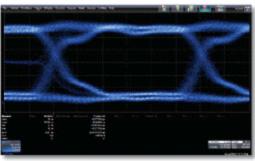

除了完成全面的测试工作外,QPHY-DDR2还可以对DDR2读写波形分别绘制眼图(如右图9所示),方便用户观察被测DDR2系统数据线上的信号完整性并对可能出现的问题进行及时观测与调试。

图9 使用QPHY-DDR2对DDR2读/写信号绘制眼图

DDR2测试示波器及探头选型

关于示波器选择方面,最低配置情况下可选择带宽2.5GHz的示波器进行测试,如选择力科SDA725Zi示波器结合QPHY-DDR2一致性测试软件包对DDR2总线进行测试。然而,对在频率较高的1066M DDR2测试时,由于其时钟频率为533MHz,对应的五次谐波、频率为2.67GHz,已经高于2.5GHz,为了捕获到其5次甚至更高次谐波成分,需要选择更高带宽的示波器。所以,对DDR2总线的测量,我们推荐使用带宽3.5G及以上的示波器进行测量,如带宽3.5GHz的力科SDA735Zi/740Zi/760Zi或带宽覆盖从4GHz到业界最高的30GHz的力科8Zi系列示波器。

对于探头系统,在进行DDR2时钟测试时,仅需要一根足够带宽的差分探头即可。在进行电气性能及时序测试时,使用两根差分探头分别测量差分时钟及DQS/DQS#信号,一根单端探头测量相应的DQ信号即可完成大部分的指标测量。 对于DDR533的DQ信号测试,建议用焊接式差分探头。 在进行某些差分信号交叉点电压等指标测量时需要使用两根探头分别测量该差分信号的正端及负端信号。对具体的探头型号,推荐使用带宽3.5GH或6GHz的力科WaveLink D320/D310或D610/D620系列可焊接式差分探头。

结语:本文简要介绍了DDR2总线,DDR2相关测试以及力科的DDR2全方位测试解决方案。力科QPHY-DDR2从信号连接,DDR2总线全面测试到测试报告生成各方面进行了完美的集成,为复杂的DDR2测试提供了最佳的测试环境,从而保证了DDR2测试的精确性与高效率。

参考文献

1. DDR2 SDRAM SPECIFICATION JESD79-2E,JEDEC, April 2008

2. QPHY-DDR2 datasheet, LeCroy Corp. July 2009