半导体C-V测量基础

中心议题:

- 半导体电容的物理特性

- 基本测试配置框图

- 紧密集成的源-测量单元、数字示波器和C-V表

- 方便集成其他外部仪器

- 基于探针的高分辨率和高精度测量

- 测试配置和库易于修改

通用测试

电容-电压(C-V)测试广泛用于测量半导体参数,尤其是MOSCAP和MOSFET结构。此外,利用C-V测量还可以对其他类型的半导体器件和工艺进行特征分析,包括双极结型晶体管(BJT)、JFET、III-V族化合物器件、光伏电池、MEMS器件、有机TFT显示器、光电二极管、碳纳米管(CNT)和多种其他半导体器件。

这类测量的基本特征非常适用于各种应用和培训。大学的研究实验室和半导体厂商利用这类测量评测新材料、新工艺、新器件和新电路。C-V测量对于产品和良率增强工程师也是极其重要的,他们负责提高工艺和器件的性能。可靠性工程师利用这类测量评估材料供货,监测工艺参数,分析失效机制。

采用一定的方法、仪器和软件,可以得到多种半导体器件和材料的参数。从评测外延生长的多晶开始,这些信息在整个生产链中都会用到,包括诸如平均掺杂浓度、掺杂分布和载流子寿命等参数。在圆片工艺中,C-V测量可用于分析栅氧厚度、栅氧电荷、游离子(杂质)和界面阱密度。在后续的工艺步骤中也会用到这类测量,例如光刻、刻蚀、清洗、电介质和多晶硅沉积、金属化等。当在圆片上完全制造出器件之后,在可靠性和基本器件测试过程中可以利用C-V测量对阈值电压和其他一些参数进行特征分析,对器件性能进行建模。

半导体电容的物理特性

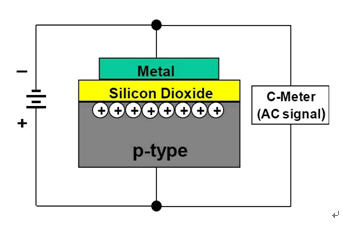

MOSCAP结构是在半导体制造过程中形成的一种基本器件结构(如图1所示)。尽管这类器件可以用于真实电路中,但是人们通常将其作为一种测试结构集成在制造工艺中。由于这种结构比较简单而且制造过程容易控制,因此它们是评测底层工艺的一种方便的方法。

金属二氧化硅电容计(交流信号)P型

图1.P型衬底上形成的MOSCAP结构的C-V测量电路

图1中的金属/多晶层是电容的一极,二氧化硅是绝缘层。由于绝缘层下面的衬底是一种半导体材料,因此它本身并不是电容的另一极。实际上,其中的多数载流子是电容的另一极。物理上而言,电容C可以通过下列公式中的变量计算出来:

C=A(κ/d),其中

A是电容的面积,

κ是绝缘体的介电常数

d是两极的间距

123下一页> 关键字:半导体 C-V测量 MOSFET JFET 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006731

因此,A和κ越大,绝缘体厚度越薄,电容值就越高。通常而言,半导体电容的大小范围从几纳法到几皮法,甚至更小。

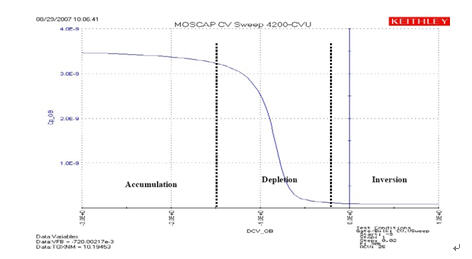

进行C-V测量时要在电容的两极加载直流偏压同时利用一个交流信号进行测量(如图1所示)。通常情况下,这类测量使用的交流频率范围从10kHz到10MHz。所加载的偏压作为直流电压扫描驱动MOSCAP结构从累积区进入耗尽区,然后进入反型区(如图2所示)。

图2.C-V测试中获得的MOSCAP结构的直流偏压扫描

强大的直流偏压导致衬底中的多数载流子在绝缘层界面附近累积。由于它们无法穿透绝缘层,因此当电荷积累在界面附近(即d为最小值)时电容在累积区达到最大值。如图1所示。从C-V累积测量可以得到的一个基本参数就是二氧化硅的厚度tox。

当偏压降低时,多数载流子从氧化层界面被排斥开,耗尽区形成。当偏压反相时,电荷载流子远离氧化层达到最大距离,电容达到最小值(即d为最大值)。根据这时的反型区电容,可以推算出多数载流子的数量。这一基本原理同样适用于MOSFET晶体管,只是它们的物理结构和掺杂更加复杂。

在偏压扫过这三个区的过程中还可以得到多种其他参数,如图2所示。利用不同的交流信号频率可以得到其他细节信息。低频可以揭示所谓的准静态特征,而高频测试则可以表现出动态性能。这两类C-V测试通常都是需要的。

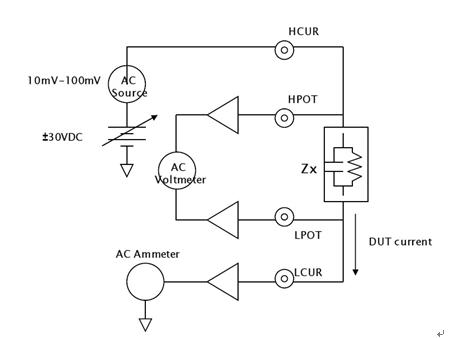

基本测试配置

图3给出了基本C-V测量配置的框图。由于C-V测量实际上是在交流频率下进行的,因此待测器件(DUT)的电容可以根据下列公式计算得到:

CDUT=IDUT/2πfVac,其中

IDUT是流过DUT的交流电流幅值,

f是测试频率,

Vac是测得的交流电压的幅值和相角。

换而言之,这种测试通过加载交流电压然后测量产生的交流电流、交流电压和它们之间的阻抗相角,最终测出DUT的交流阻抗。

交流源

交流伏特计

DUT电流

交流安培计

图3.C-V测量的基本测试配置

这些测量考虑了与电容相关的串联与并联电阻,以及耗散因子(漏流)。图4给出了这类测量可以测出的主要电路变量。

<上一页123下一页> 关键字:半导体 C-V测量 MOSFET JFET 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006731?page=2

<上一页123下一页> 关键字:半导体 C-V测量 MOSFET JFET 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006731?page=2 z,theta:阻抗与相角

R+jX:电阻与电抗

Cp-Gp:并联电容与电导

Cs-Rs:串联电容与电阻

其中:Z=阻抗

D=耗散因子

θ=相角

R=电阻

X=电抗

G=电导

图4.C-V测量得到的主要电气变量

成功C-V测量的挑战

C-V测试配置的框图虽然看上去非常简单,但是这种测试却具有一定的挑战。一般而言,测试人员在下面几个方面会遇到麻烦:

•低电容测量(皮法和更小的值)

•C-V测试仪器与圆片器件的连接

•漏电容(高D)的测量

•利用硬件和软件采集数据

•参数提取

克服这些挑战需要仔细注意所用的技术以及合适的硬件和软件。

低电容测量。如果C较小,那么DUT的交流响应电流就较低,难以测量。但是,在较高的频率下,DUT阻抗将减小,从而电流会增大,比较容易测量。半导体电容通常非常低(低于1pF),低于很多LCR表的测量范围。即使那些声称能够测量这些小电容值的测试仪可能也会由于说明书晦涩难懂而很难判断最终的测量精度。如果无法明确给出测试仪整个量程的精度,那么用户需要因此而咨询制造商。

高D(漏)电容。半导体电容除了C值较低之外,还具有泄漏的特点。当与电容并联的等价电阻太低时就会出现这种情况。这会导致电阻性阻抗超过电容性阻抗,C值被噪声所淹没。对于具有超薄栅氧层的器件,D的值可能大于5。一般而言,随着D的增大,电容测量的精度迅速下降,因此高D是实际使用电容计的一个限制因素。同样,较高的频率有助于解决这一问题。在较高的频率下,电容性阻抗较低,使得电容电流较高,更容易进行测量。

C-V测量的互连。大多数测试环境下,DUT都是圆片上的一个测试结构:它通过探测器、探针卡适配器和开关矩阵连接C-V测试仪。即使没有开关,仍然也会使用探测器和大量的连线。在较高的频率下,必须采用特殊的校正和补偿技术。通常情况下,这是通过组合使用开路、短路或者校准器件来实现的。由于硬件、布线和补偿技术非常复杂,因此经常与C-V测试应用工程师进行交流是一个好的办法。他们擅长使用各种探测系统,克服各种互连问题。

获取有用的数据。除了上述的精度问题,C-V数据采集中实际需要考虑的因素包括测试变量的仪器量程,参数提取软件的多功能性和硬件的易用性。一般而言,C-V测试已仅限于约30V和10mA直流偏压。但是,很多应用,例如LDMOS结构的特征分析、低k夹层电介质、MEMS器件、有机TFT显示器和光电二极管,需要在较高的电压或电流下进行测试。对于这些应用,需要单独的高压直流电源和电容计;高达400V的差分直流偏压(0到±400V)和高达300mA的电流输出是非常有用的。在C-V测试仪的HI和LO端加载差分直流偏压能够更灵活地控制DUT内的电场,这对于新型器件的研究和建模是非常有用的,例如纳米级元件。

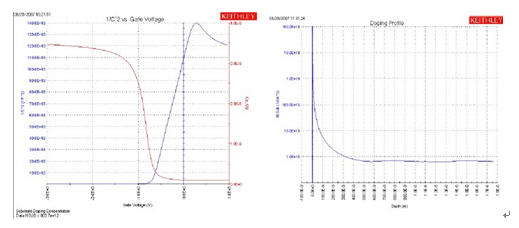

仪用软件应该包括无需用户编程可直接使用的测试例程。这些应该适用于大多数广泛使用的器件工艺和测试技术,即本文前三段中提及的有关内容。有些研究者可能会对一些不常见的测试感兴趣,例如对MIM(金属-绝缘体-金属)型电容进行C-V和C-f扫描,测量圆片上的互连小电容,或者对双端纳米器件进行C-V扫描。利用自动绘图功能能够方便的实现参数提取(例如,如图5所示)。

图5.利用吉时利4200-SCS进行参数提取的实例表现了半导体的掺杂特征(左边的蓝线),它与1/C2与Vg的关系呈倒数关系(红线)。右图给出了掺杂分布,即每立方厘米的载流子数与衬底深度的函数关系。

通常,人们都希望工程技术人员和研究人员在几乎没有任何仪器使用经验或培训的情况下就能够进行C-V测量。具有直观用户界面和简单易用特征的测试系统使得这一点成为现实。其中包括简单的测试配置、序列控制和数据分析。否则,用户在掌握系统方面就要比采集和使用数据花费更多的时间。对测试系统其它考虑因素包括:

•紧密集成的源-测量单元、数字示波器和C-V表

•方便集成其他外部仪器

•基于探针的高分辨率和高精度测量(直流偏压低至毫伏级,电容测量低至飞法级)

•测试配置和库易于修改

•提供检测/故障诊断工具帮助用户确定系统是否正常工作

<上一页123 关键字:半导体 C-V测量 MOSFET JFET 本文链接:http://www.cntronics.com/public/art/artinfo/id/80006731?page=3