串联电感--连接器怎么产生电磁干扰

中心议题:

- 产生电磁干扰的原因

- 有效减少连接器辐射的准侧

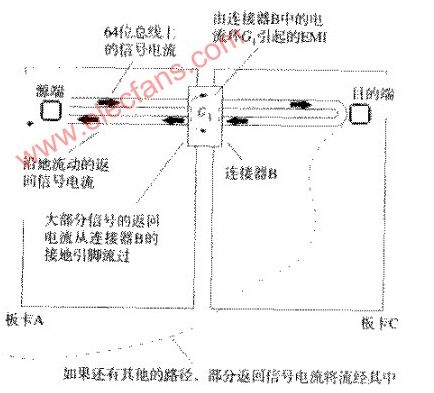

一个64位总线从板卡A经过连接器B连到母板卡上,母板卡可能是一个主CPU卡或是一个通往其他子卡的无源通道。64条信号线的返回电流从母板卡C流回板卡A,其中的绝大部分通过了连接器B的接地脚。

图1 一个64位总线信号的返回电流

只有一小部分信号返回电流经由不同的路径流回板卡A然而,正是这一小部分返回电流引起了大量的EMI问题。

高频电流流经大的环路时会辐射出大量的电磁能量,这将不能通过FCC或VDE所规定的辐射测试。EMI 设计的主要工作是使所有信号的电流环路横截面的面积最小。例如,在一个完整地平面上,高频电流趋向于紧贴走线正下方返回,一条

这么大的环路面积,在EMI方面是可以接受的。在图1中,板卡A和C上的64位 总线信号由完整地平面返回,因此我们可以忽略其信号和地之间的环路面积。

返回电流路径上的任何阻断或不连续,如连接器接地引脚上的转换,会在电流环路上产生“气泡”,这些气泡是否会带来足够大的面积,从而导致辐射超标,取决于回路中信号电流的总DI/DT值。

在图1中,环路面积上的气泡一般发生在连接器B内,因为连接器上的信号和地线引脚是分开的。该气泡记为G1,64位总线信号路径的环路电感大部分来自环路G1的电感。

信号返回电流是否有其他的返回路径,取决于连接器B的物理结构,以及板卡A和C所在的机箱结构的具体情况。任何电流在返回位于板卡A上的源端时,如果不经过连接器B,则将包含一个大的环路面积,并产生大量的辐射。

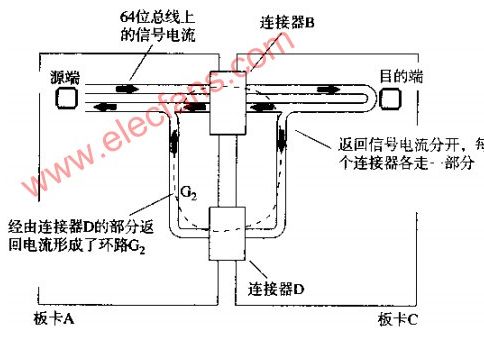

例如,在图2中,假设板卡A和C共用两个连接器,另外增加的连接器记为D,将其安排在与连接器B相隔一段距离的地方。现在有一部分信号的返回电流可以由连接器D上的地线流加A,如图9.7中的环路G2所示。

图2 通过连接器D转向的返回电流

123下一页> 关键字:连接器 电感 电磁干扰 本文链接:http://www.cntronics.com/public/art/artinfo/id/80009765

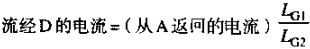

调整信号返回电流通过连接器D的比例,取决于环路G1的电感(见图1)与G2(见图2)的电感的比值:

(式5)

(式5)

在非常低的频率上,流经连接器D的信号返回电流的量取决于阻抗的比值,而在较高的频率上,则取决于上式中电感的比值。即然EMI是一个高频问题,这里我们也就只关心两个环路电感的比值。

因为环路G1面积较小,其电感也比G2要小一些,因此只有一小部分的返回信号电流经过路径G2。但是, 即便如此小的一部分电流也足以使辐射超标。在30MHZ以上,在距设备

要想精确计算一个数字产品的辐射强度等级是件不现实的事情,因为有太多的因素会影响结果。下式表示了一个简单的约束条件:开放的测量试验场合,30MHZ以上,满足FCC和VDE辐射限制的环路面积、峰值电流和上升时间。

(式6)

(式6)

其中:E=

A=辐射环路面积,IN2

IP=峰值电流,A

T10~90%=信号上升时间

FCKOCK=时间频率,HZ

关于上式需要注意:

最终产品的辐射指标与上式所预算的指标相差20DB是很常见的,其中包括一个很大的修正系数。

应该明确,辐射测试是测试系统中所有线路辐射的总和,如果一条线刚刚符合标准,那么增加了100条线肯定就不符合标准了。在设计最后设定之前,先搭建一个模拟系统测试一下,其中只需包括一些穿过连接器系统的时钟信号,听起来很浪费,但最终来看会节省很多钱。因为等到工程结束需要重新设计机械封装和屏蔽时,成本会急剧增加。

例:一个连接器的噪声辐射

图1显示了一个典型的16位总线。我们来分步计算路径G1和G2的电感,以及路径G1的辐射和路径G2的辐射。

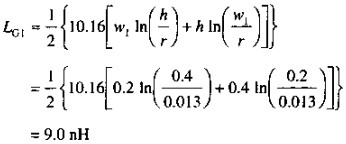

路径G1的电感:

(式7)

(式7)

R=0.025/2(引脚半径,直径的一半,IN

注意:我们用的是H/R,而不是2H/D)

W1=0.2(信号到地的距离,IN)

H=0.4(连接器引脚长度,IN)

1/2=修正系数,由于信号引脚两边有地线

路径G2的电感:

(式8)

(式8)

R=0.025/2(引脚半径,直径的一半,IN)

W1=0.2(信号到连接器D的距离,IN)

<上一页123下一页> 关键字:连接器 电感 电磁干扰 本文链接:http://www.cntronics.com/public/art/artinfo/id/80009765?page=2

H=0.4(连接器引脚长度,IN)

假设每个驱动信号都通过50欧传输线传播,幅度为典型的TTL电平3.7V,信号电流的峰-峰值为74MA。峰值电流是其一半或正负37MA。

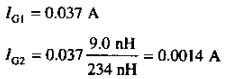

采用式5救出路径Y的峰值电流:

(式9)

(式9)

现在采用式6来估算环路G1和G2的辐射,首先计算G1:

![]() (式10)

(式10)

A=0.08(引脚长度

IC1=0.037(峰值电流,A)

T10~90%=5*10的-9次方(信号上升时间,S)

FCKOCK=100MHZ

一条信号线的辐射为82UV,总的辐射与相关信号线数量的平方根近似成正比,所有16条线的辐射量为:

![]() (式11)

(式11)

按照这样的设计,这个连接器的安排将不能通过规定测试,再看看连接器D的情况:

![]() (式12)

(式12)

A=2.4(引脚长度

IG2=0.0015(峰会值电流,A)

T10~90%=5*10的-9次方(信号上升时间,S)

FCIOK=100MHZ

一条信号线的辐射为90UV,所有16条线总的辐射为:

![]() (式13)

(式13)

实际上,环路G2辐射比G1辐射大,这里因为电感LG2只随连接器B与D之间距离的对数值的增加而增 加,而环路G2面积的增加直接正比于连接器B和D的距离。电感的增加虽然使得流过G2的电流减少,但是环路面积增大导致增加的辐射要大得多。连接器B和D 之间距离的增大实际上会使辐射问题更加恶化。

下面是一些能有效减少连接器辐射的准则:

准则1 在连接器B中多用一些接地引脚,使地线靠近每一条信号线,从而有效地减小连接器B中的有效辐射环路面积。

准则2 在连接器B中增加更多的地线也能降低其电感,由式5可知,这样可以减少在远端环路中流过的电流。

准则3 将板卡A上所有的母板卡连接器紧密放置,以破环或消除远端返回电流路径。

准则4 沿着板卡A和板卡C的边缘布放连续的接地点,根据式5这样可以提供一个阻抗非常低的返回路径,降低远端环路电流。

准则5 不要把I/O电缆连接在板卡A的外边缘上,这样会从母板卡C上产生一个大的远端返回电流路径,经过大地和I/O电缆返回板卡A。应该将电缆边在母板卡上,或者在母板卡上靠近连接器B外进行高频滤波。

准则6 对于采用的驱动门电路,要使其上升沿时间要尽可能长。式6表明,辐射与上升时间的倒数成正比。

<上一页123 关键字:连接器 电感 电磁干扰 本文链接:http://www.cntronics.com/public/art/artinfo/id/80009765?page=3