多层压敏电阻阵列的滤波连接器设计

中心议题:

- 滤波连接器设计

- 压敏电阻设计

- 多层平面电容阵列设计

- 多层压敏电容阵列设计

“连接器对于电子设备没有什么贡献”是一个陈旧的和有争议的说法,写出来后引起了一些争论,但现在毫无疑问已经是过时和错误的!目前单个的连接器,能对抗连续的或瞬态的噪声实现设备保护功能。当然,随即而来的就是费用问题。加上滤波功能,一个10美元的连接器就成为一个100美元的连接器。加上防电压尖峰功能,你就需要面对1000美元的连接器了。

幸运的是,近来的革新已经改变了这个令人困惑的局面。多层平面阵列的滤波式电容器,现在可实现如瞬态保护的功能。采用多层压敏电阻平面阵列起瞬态保护的滤波连接器为产品设计提供了一个可选方案。

压敏电阻

压敏电阻就是可变电阻。在较低的应用电压时,压敏电阻充当一个传统的高阻值电阻并服从欧姆定律,当超过一定的阈值电压后,该器件变得高度导电,在高电压时表现出低的阻抗。当压敏电阻导电时,它钳位外加电压到指定的最大值,该值是设备可以承受的。凭借这些特性,压敏电阻在电子产品中得到应用,保护电路远离瞬间过电压。在低电压时,压敏电阻类似于一个陶瓷电容器,正因为如此,它可以当作处理连续噪声的滤波器的一部分。那么,为什么压敏电阻器不经常使用在滤波应用中,使他们能够完成双重角色——即连续噪声衰减和瞬态电压抑制器呢?

压敏电阻脉冲等级

当把压敏电阻器用作滤波应用时,其限制之一是:其保护功能降级,这可能是电压浪涌重复性冲击的结果。

压敏电阻器是由陶瓷材料制成的。多数压敏电阻其主要成分是氧化锌(ZnO)。同时添加了少量其它氧化物,如铋,钴,锰等。因此,压敏电阻有时被称为金属氧化物压敏电阻或MOVs。

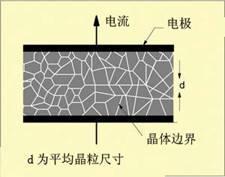

在制造过程中,原始的陶瓷粉末进行混合、成形,然后烧制。并用金属化来实现电气连接。在陶瓷的烧制过程中,形成了多晶结构(图1)。添加的金属氧化物移动到结晶体的边缘,形成半导电层P-N结。这意味着平均晶粒尺寸由原始粉末配方和烧制温度来决定。当单位晶粒边界的外加电压低于3.6伏特时,晶粒边界呈现高的电阻性。高于上述门限后,将进行切换变成高的导电性。

图1

压敏电阻本身的切换电压取决于电极间平均晶粒的数目。

压敏电阻的晶体结构没有方向性,因此,压敏电阻是双极性器件。它们表现出的电子特性,如对称性、尖峰电压击穿特性,类似于背对背齐纳二极管。传统的看法认为压敏电阻在高电流重复脉冲下会导致电气性能的降级,(特别是降低了其钳位性能,增加了它们的漏电流)。有一段时间,压敏电阻制造商要求使用大晶粒的陶瓷成分。大晶粒尺寸使得单位面积的电极有更少的晶体边界和电极之间有更长的电流路径。单位面积电极上的串联电阻相对较高,导致成比例地降低峰值电流的容量。

对在低电压下工作的压敏电阻表面贴装片,要求使用精细晶粒陶瓷成分,这个需求可以在多层结构下实现。当这一目标完成后,相对于多层结构提供的元件表面,连接到大电极面积上的细小和均匀的晶粒使得单元元件体积内峰值电流容量大幅的增加。

多层压敏电阻器(MLVs)的电流和能量比相对于其它压敏类型是非常稳定的,现在能够展示MLVs可以经受住成千上万次全额定电流峰值冲击,而性能不降级。

速度与过冲

各种瞬态保护技术的元件制造商希望采用他们喜欢的产品,反应速度、或不采用往往成为压敏电阻考虑的问题。压敏电阻基底材料的响应时间要远远少于500皮秒。

部分早期压敏元件反应时间降低的主要因素是成品封装时引起的寄生电感。在结构中使用了25至50毫米的引线,其表现出0.6nH/mm的电感,而高自感形成径向导线压敏电阻的特性。

现在,多层结构已消除引线,一个典型的电感为1200pH量级的1206MLV芯片的响应时间不超过1纳秒。其他元件的配置,如果成为滤波电容器的结构,对于压敏电阻是合适的,其等效串联电感(ESLs)应低至30pH。这些为响应时间下降到几十皮秒提供了可行性。

压敏电阻结构中固有自电感(L)所造成的另一个问题是电压过冲。由于压敏电阻自感(L)的原因引起变化的电流(di/dt),会产生-Ldi/dt的电压。在电压尖峰,压敏电阻器上将出现一个过冲(钳位电压和压敏电阻自感产生的感应电压之和)。减少MLV滤波器结构中自感到数十pH,可以消除所担心的电压过冲。

EMI滤波器

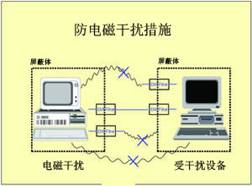

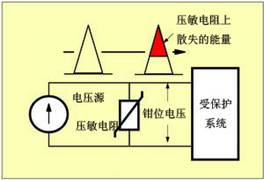

针对辐射有效的措施是屏蔽。辐射噪声能量被屏蔽体吸收并以热的形势散失。针对传导有效的措施是EMI滤波器,将传导能量从受保护系统转到地里。(图2)。EMI滤波器由电容器和电感器组成,利用其不同的阻抗特性,来选择性的减少不必要的信号。

图212下一页> 关键字:压敏电阻阵列 滤波连接器 连接器 本文链接:http://www.cntronics.com/public/art/artinfo/id/80010933

滤波器是双向的。它阻止不想要的信号远离系统,同时也阻止该系统向外发射噪声。现在一个比较普遍的做法是将滤波器装在设备的电路板上,但最有效的还是将滤波器放置在设备屏蔽体的出口和入口。连接器可以将电源和信号电缆并在一起,这样它们进入设备屏蔽体只在一个点处。在连接器内每一个接触的地方,都可以形成一个滤波器,根据系统的要求可以是C,T,L或Pi型结构。因为滤波连接器的使用可以去掉电路板级的滤波器电路,从而可降低整个系统的尺寸和重量。同时,由于焊点数量的减少,系统的可靠性得到提高。

多层平面电容阵列

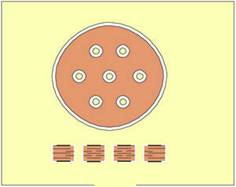

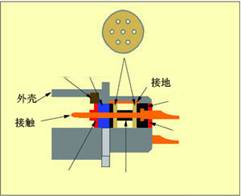

多层平面阵列是一种特定的用于EMI滤波连接器的元件设计形式。一个陶瓷块内包含有多种电容器。单个接线都是通过通孔连接到每个电容器,并且在器件范围内都连接到地。当信号沿多条路径到地时表现出非常低的阻抗(图3)。连接器的每一个接头连接到一个或多个阵列内的孔上。在每一个孔里有一个电容器——‘热电极’与周围的整体连接起来,地面电极覆盖整个平面并且和连接器外壳通过平面周边连接起来(图4)。

图3

图4(原文图上文字看不清楚)

以平面为基础的滤波连接器适用于所有MIL-STD连接器设计。连接器的形状(该平面阵列的外形必须一致)均为圆形或长方形。常用的矩形设计包括D-Sub和高密度D-Sub和微Ds,Arinc404s和Arinc600。不规则形状也可以。相应的平面尺寸是:从5毫米见方到75毫米直径。

接触数目从2个到200多个。标准的接触范围从0.3毫米直径向上到同轴电缆——全部能滤波。标准接触程度从0.63毫米开始。

平面阵列内,有多达6种不同的、没有任何比率关系电容值可以布置在版面上。每一个平面可以指定不同的工作电压,一个典型300伏额定直流电的平面可以承受高达750伏的瞬态峰值。瞬态能力达3000V需要指定。个别的孔可能是绝缘的(馈入点)或接地。可以指定最大为10MΩ的地平面电阻,并且串扰电容可以限制在10pF或更小。

平面阵列的复杂性不在于复杂的电气要求以便组成单个元件,而在于制造该器件的机械精度。典型情况下,连接器的引脚位置精度必须优于±0.05毫米,而平面阵列必须有相同的或更好的公差。平面必须在陶瓷煅烧之前完成(成形和钻孔),在煅烧时它们会收缩,一般是百分之二十左右。30毫米直径平面煅烧后引脚的位置相对于中心基准点移动至少超过2.5毫米,也就是说它是管脚公差允许值的50倍!

平面阵列是一种最先进的无源器件。每个器件拥有多个电容器,多个电容值以及多种电气功能的替代品,它就是一种原始的集成无源元件。

多层压敏电容阵列

低电压时多层压敏电阻的效能像电容器。晶体颗粒的边界是绝缘的,表现出介电材料特性。MLV的有效介电常数约800,是典型的X7R多层电容器介质介电常数的四分之一到三分之一。从压敏变阻器得到的电容值是低于那些传统的电容器。鉴于这些是常规多层电容器技术所能得到的低端产品,从总价值看,MLV的滤波性能与一个电容器相比是无区别的。

当应用于滤波器时,压敏电阻提供了额外的瞬态保护功能。它将暂态电压脉中所载的能量消耗成热(图5)。高导电氧化锌颗粒作为散热器可确保整个器件中迅速和均匀地散热,并尽量减少温度上升(但是压敏电阻只可以消耗少量的平均功率,不适合应用在连续功率消耗上)。

图5

已有事实表明,可以建造一种多层结构,不具有多层电容元件结构,因而不能重复用作压敏电阻。这些复杂的组成部分纳入到起保护作用的EMI滤波连接器(包括插头和插座)和滤波适配器。他们可以用于取代或补充在C,L,T或Pi滤波器结构中的电容器。<上一页12 关键字:压敏电阻阵列 滤波连接器 连接器 本文链接:http://www.cntronics.com/public/art/artinfo/id/80010933?page=2