基于SAW技术的车辆自动识别系统的实现

中心论题:

- 系统组成及工作原理

- 硬件电路设计

- 系统软件设计

- 系统测试

解决方案:

- 询问单元设计和信号后处理单元设计

- 系统软件设计

车辆识别系统的研究起始于二十世纪70年代,最早采用光学与红外技术, 其环境适应性较差,且车辆的最大车速限制为70km/h,已逐渐被淘汰。

SAW技术是一种新兴的识别技术。它采用编码的SAW传感器作为ID标签,无任何连线,具有低能耗﹑抗干扰能力强﹑体积小等优点,特别适用于强电磁干扰环境下高速运动车辆的非接触式测量。

本文设计了一种基于SAW技术的车辆自动识别系统, 可应用于不停车车辆识别,为高速公路车辆收费系统提供了一种高效的解决方案,车辆识别距离10m,最高车速120km/h。识别码长度32位,可识别的车辆数目为232。该系统可全天候工作于野外环境中。

系统组成及工作原理

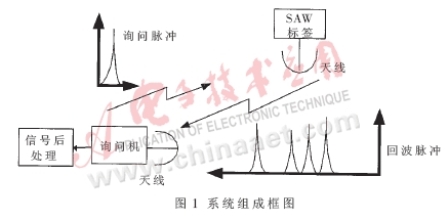

SAW传感器构成的车辆识别系统由一个装载在高速运动车辆上的SAW传感器标签、一个带主动式天线的询问单元和一个信号后处理单元组成。如图1所示。

SAW标签由传感器天线、压电基片、叉指换能器和经传感器体外编码的反射极组成。

传感器天线接收由远处询问机发送来的询问电磁脉冲信号,通过叉指换能器转化为声表面波,遇到反射条后形成回波,回波通过叉指换能器重新转化为电磁波并再次通过天线发射出去。这些回波信号形成了由晶体表面的反射条的数目和位置决定的脉冲序列,它类似于条形码图案,每个脉冲的时间延迟取决于SAW传播速度。信号后处理单元对脉冲延迟变化进行估计,实时解调出识别码。

硬件电路设计

a.询问单元设计

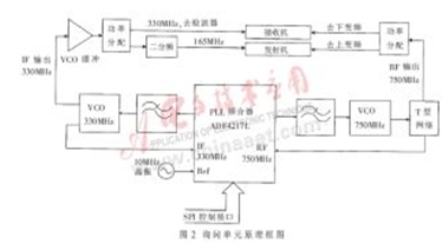

图2为询问单元方框图。它由发射机、接收机、本地振荡模块等部分组成。

本地振荡模块:在本系统中共需要三个频率,即750MHz、330MHz和165MHz,它们由频率综合器产生。频率综合器采用AD公司的ADF4127L,它是一款电流型双频频率合成器,能同时提供射频/中频两个频率, 采用SPI接口控制,通过FPGA****??对其内部寄存器进行配置。

ADF4127L产生的输出频率,被VCO锁定在330MHz和750MHz。330MHz的VCO采用MAX2608,它可产生300MHz~500MHz的频率;750MHz的VCO采用Mini公司的Pos-1050型,频率范围为685MHz~1025MHz。

750MHz信号经功率分配器分别提供给发射机的上变频和接收机前端的下变频部分。330MHz信号一路提供给接收机的检波器,另一路经二分频产生165MHz频率。功率分配器选用Mini公司的LRPS-2-4J,具有很低的电压驻波比。二分频选用Microwave公司的低噪声二分频器HMC361S8G。

发射机:FPGA产生40ns的时间窗截取165MHz的载波,将其频谱展宽,产生中心频率为165MHz、带宽为50MHz的脉冲信号,并送到SAW扩展器,形成一个线性调频脉冲。SAW扩展器采用南京54所生产的声表面波色散延迟线,带宽为20MHz,经过扩展后的脉冲只有20MHz带宽,扩展器衰减30dB。此信号经过中频放大器AD8353放大后,与750MHz本振进行上变频到915MHz,经射频带通滤波器滤除带外杂波,再经MAX2235进行功率前置放大,由天线发射出去,形成询问信号。上变频芯片选用MAX2671,其射频输出范围400MHz~2500MHz。射频带通滤波器采用F5CE-D2系列的SAW带通滤波器,它使用了特殊的DMS双模SAW技术,具有很好的带外衰减和通带平坦度,广泛应用在移动通信中。

询问信号发射完毕后,天线开关立即打到接收位置,为接收做好准备。转换开关采用Mini公司的KSWHA-1-20,它是一种GsAs开关,具有很高的隔离度,开关转换速度3ns。

接收机:采用了超外差式接收机的设计方案,如图3。

回波信号到达接收机前端时,首先经过滤波处理。在接收机中有两个射频滤波器:预选择滤波器和镜像抑制滤波器。预选择滤波器滤除掉无用信号,以防止射频前端发生饱和并产生交调失真。镜像抑制滤波器抑制第一镜频、半中频和本振杂散响应。射频滤波器选用FAR-F5CE-915M00-D236。滤波处理后,信号通过射频放大器MAX2642进行放大,它是低噪声放大器,在1.3dB的噪声系数条件下,提供0dBm的输入IP3。

经过射频滤波和放大后,信号与本振750MHz进行下变频。下变频芯片选用MAX2682,它采用双平衡混频器结构,输入频率400MHz~2500MHz。下变频后,信号进入中频SAW滤波器进行中频滤波,再通过SAW压缩器,输出被压缩的脉冲。被压缩的信号经过AD8353中频放大,送入正交下变频,解调出I、Q两路信号。RF2721是RF公司为数字移动接收机设计的正交解调器,它从放大和滤波后的中频信号中恢复同相及正交的基带信号。

b.信号后处理单元设计

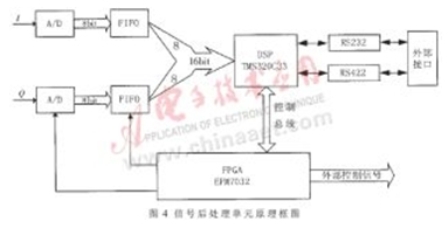

信号后处理单元的原理框图如图4所示。

从询问单元送来的经过正交下变频的同相分量I和正交分量Q,经低通滤波器滤掉高频分量,再经过8位模/数转换器AD9058转换为数字量,经FIFO缓存,送至DSP进行运算。FIFO选用HBA公司的FQV251,DSP选用TI公司的浮点处理器TMS320C33。I、Q信号是接收机送出的解调信号,它携带了识别卡的识别信息,识别码的格式为32位。时钟同步时,采用软判决的相关处理算法,即根据两路信号的平方和是否超过门限判断当前位是0或1。

FPGA负责各种控制信号的产生,选用ALTERA公司MAX7000系列的EPM7032,可提供5000个可用门。EPROM选用ST公司的27C256。

系统软件设计

软件流程如图5所示。系统开始工作后,DSP初始化,FPGA配置频率综合器ADF4127L,产生精准的频率源。询问机转换开关指向发射位置,发射单元发射询问脉冲信号,经过一段时间后,开关指向接收位置,接收单元接收回波信号,先进行A/D采样,并将I路和Q路的采样值平方相加,若大于编码门限,则判定当前码为1,否则为0。一帧32位识别码判别完后,询问单元重新发出询问信号,如此循环。解调出的识别码通过串口送给外部设备,以供处理。

系统测试

本系统在高速公路收费站和停车场做了多次测试。测试结果表明,本系统可以全天候工作,在10m距离内可以准确地识别出高速运动车辆,加快了车辆通过收费站的速度,在一定程度上缓解了交通紧张状况,降低了收费站成本。