降低高速DSP系统设计中的电源噪声

中心议题:

- 如何降低交扰

- 降低锁相环(PLL)引起的干扰

- 适当地应用电容器是降低噪声的有效方法

- 降低交扰的技术有:线迹间距加大,增加地线,降低谐波分量和线迹端接技术

- 采用合适的滤波器和稳压器,分离模拟和数字地是降低PLL干扰的方法

- 选择合适电容值并注意一些应用电容器的方法

降低交扰

交扰是一个重要的噪声源。在高速系统中,信号地通路依赖于工作频率。对于低速信号(<10MHZ),电流经过最小电阻地通路(最短通路)返回到源。

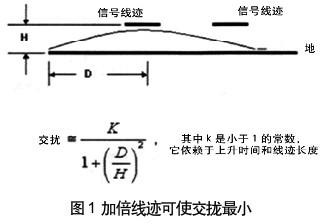

在10MHZ以上,情况就不同。经电流最小电感地通路返回。重要的是返回信号以电流分布传播(图1),这意味着相邻信号的返回通路可能容易重叠,导致交扰。

降低交扰的技术有:线迹间距加大,增加地线,降低谐波分量和线迹端接技术。

在高速DSP系统中,加倍信号间的线迹间距,可降低环路重叠,使交扰降低4倍。对于差分信号(Earthnet或USB),建议间距所产生的信号对应具有所需的匹配阻抗。另外,关键信号(即时钟)应屏蔽,路由信号在电源和地平板之间的内层,或把一个地平板放置在关键信号下面层上。

在再制板上加信号线时,应包括一个并联地线。这可能提供高速电流返回通路并在电流环路中产生最小面积。这个附加的通路,确保返回电流不产生大的环路和拾取噪声。

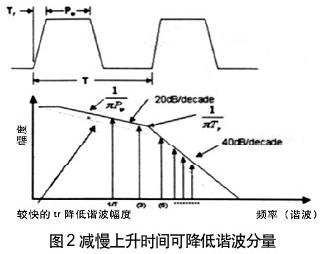

在降低交扰时,评价快速沿所引起的谐波和干扰是重要的。例如,在线迹上增加串联终端电阻器,会使上升时间(Tr)减慢,这是有效地降低谐波分量的方法。噪声幅度曲线在低频能较好地衰减谐波分量(图2)。

线迹可做为传输线(在上升时间Tr小于2倍传播延迟时)。因此,应保持线迹尽可能的短。若线迹的长度足以做为传输线,则用串联终端(电阻器与输出驱动器串联)或并联终端(在负载处电阻器到地)接线。若电阻器与所用线迹PCB阻抗匹配,则可以降低传输线反射和瞬变。

锁相环

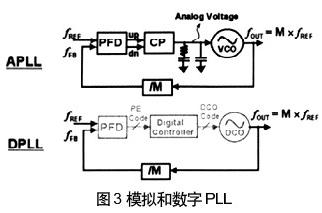

锁相环(PLL)是另一个重要的噪声源。在某些DSP中正日益采用模拟和数字版本PLL(图3)。隔离到PLL电源时,用π形滤波器去除高频噪声是有效的。但它对去除低噪声作用不大,需要用多级滤波器网络。然而,在快速开关电路中,一个低压降(LDO)稳压器是更适合的,因为这种器件在低频具有高电源抑制比(PSRR)。若设计的系统运行在噪声环境(如汽车、电/机装置),具有较大的低频瞬变,则应选择高PSRR稳压器。

分离模拟和数字地对于隔离来自模拟部分的数字噪声有帮助。对于低速电路这样做也是良好的。然而,对于高速电路(例如视频部分)应避免分离地。快速开关电流需用最小的电流环路,而隔离地阻止来自选择通路的电流。因此,将选择另外通路到源,这最终导致势差、电流流和辐射。在数字数据进入点把模拟和数字地短接在一起,可提供一个直接通路而不影响低频信号。信号朝实际的最短返回路径到源,而不是短路的通路。

电容器应用

适当地应用电容器是降低噪声的有效方法。去耦电容器提供一个低阻抗到地通路来旁路不希望的高频能量。可以用体电容器来旁路低频到地,以及用去耦电容器提供本地电荷存储。

对于去耦电容器没有最好的值,这是因为反作用影响。通常,电容器阻抗随频率和电容降低。当信号频率超过谐振频率时,电容器变成电感而不再是一个有效的滤波器。尽管低阻抗和更多电荷存储能降低下降,但对于高频信号,高值电容器不是最佳的。理想地,在电源地应包含一个高值和一个较低值电容器。若不能实现,用一个0.01礔电容器是一个可接受的折衷方案。应该用较对大的体电容器,至少10倍于总去耦电容器。

例如,在100KHZ,100礔电解电容具有0.6Ω左右的等效串联电阻(ESR),同样值的钽电容具有0.12Ω左右的ESR,这使得钽电容更适合体电容器。对于去耦陶瓷电容优于聚酯电容器。例如,在1MHZ,0.1礔陶瓷电容器具有0.12Ω左右的ESR,而1.0礔聚酯电容器具有0.11Ω的ESR。

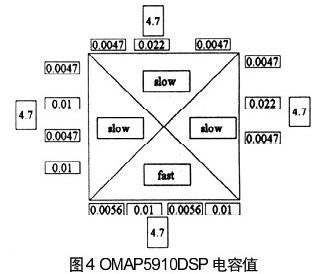

去耦电容器应放置在PCB底端靠近器件引脚处。对于高速DSP,去耦电容器应放置在每个电源引脚处。若空间不允许这样做,也应尽可能地放置在器件周围。复杂DSP去耦的一种有效方法是从对角划两个虚线构成一个X(图4)。然后独立分析4个区域的每个区域。

为使得体电容器靠近去耦电容器,把它们放置在板的顶端。这种定位使线踪最短,同时可降低辐射和寄生电感。

以TI公司的OMAP5910 DSP为例,特别注意包含数字PLL和外部存储器接口的区域(图4中左边区域)。该器件有13个芯核电压引脚,峰值芯核电流耗电170mA(平均每个引脚13mA)。在该区域的3个芯核电压引脚包括数字PLL和外部存储器接口,耗电39mA。为了保证精度,在确定电容器大小时,增加100%容限(即78mA)是合适的。必须消除峰值I/O电流。应采用谨慎的方法,假定在此区域所有54个I/O线同时开关4 mA,这将导致216 mA通过此区域的8个I/O电压引脚。

随着芯核和I/O电压工作不同频率,必须用合适大小的电容器去耦电源。在此实例中,用下面的公式计算,计算的芯核电容为0.0078礔,对于216mA I/O 电流所需电容为0.22礔:C=I(dv/dt)

其中I为峰值电流,dv为最大所允许的纹波电压(假定10mV),dt为上升时间(假定1ns,OMAP5910典型值)。

所以,芯核电容C=78mA×(1ns/10mv)=0.0078礔

在OMAP5910 BGA 封装中,对于每个区域的4个电容器都有足够的空间,没有一个是用于每个芯核电源引脚的。因此,为了去耦芯核电压引脚,最好选择两个电容器,其总值为 0.0078礔(配置两个0.0047礔陶瓷电容器,以使从引脚到地有最短距离)。

必须考虑开关频率。芯核部分在150MHz开关转换,而8个I/O引脚在75MHz开关转换。可以用另外两个电容器位置来去耦I/O电压引脚(即用两个自谐波振频率75MHz以上的0.01礔陶瓷电容器提供0.022礔)。

体电容器值

在此实例中,DSP总芯核电压电流为338mA。用上面的公式计算电容为0.0338礔。做为体电容应该是10倍去耦电容值,大约为0.39礔。对于I/O电压,进行同样的处理,得到0.84礔电容,给出总电容1.23礔。对于体电容器,每个提供3.075礔(1.23礔除以4,然后乘以10),应该把它加到每个区域上。现在可得到的最小体电容值是做为表面贴装元件的4.7礔,此电容值在本例中工作良好。如果没有表面贴装电解电容,应选择钽体电容器。对于4个区域的每个区域去耦和体电容值可以用这种方法计算,并示于图4。

关键字:DSP 电源噪声 交扰 锁相环 PLL 去耦/体电容器 本文链接:http://www.cntronics.com/public/art/artinfo/id/80001704