减少峰值EMI解决方案

中心议题:

- 减少时钟、数据总线峰值EMI解决方案

- 使用SSFTG进行频率选择

- 与扩展频谱定时信号对比分辨

- 对减弱的波形进行调制

在系统中,EMI不仅在各类时钟线路中发生减弱,还在所有与时钟同步的信号中减弱。而且,使用此技术的好处也随着系统中地址和数据总线数量的增加而不断增加。

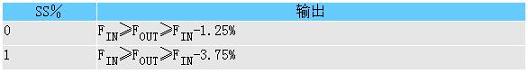

W181系列的主要特点有:在输出端产生最优的经减弱的EMI时钟信号;输出频率选择;可向下扩展-1.25%或-3.75%的输入;内部集成了环路滤波器元件;3.3V或5V工作电压;8引脚SOIC或14引脚TSSOP封装。

W181系列的主要特点有:在输出端产生最优的经减弱的EMI时钟信号;输出频率选择;可向下扩展-1.25%或-3.75%的输入;内部集成了环路滤波器元件;3.3V或5V工作电压;8引脚SOIC或14引脚TSSOP封装。 关键技术规范有:工作电压:VDD=3.3V±5%或VDD=5V±10%;频率范围:28MHz≤Fin≤75MHz;晶振基准频率范围:28MHz≤Fin≤40MHz;周期偏差:300ps(最大);可选扩展比率:-1.25%或-3.75%;输出占空比:40/60%(最坏情况);输出上升及下降时间:5ns(最大)。

关键技术规范有:工作电压:VDD=3.3V±5%或VDD=5V±10%;频率范围:28MHz≤Fin≤75MHz;晶振基准频率范围:28MHz≤Fin≤40MHz;周期偏差:300ps(最大);可选扩展比率:-1.25%或-3.75%;输出占空比:40/60%(最坏情况);输出上升及下降时间:5ns(最大)。

管脚排列与管脚功能

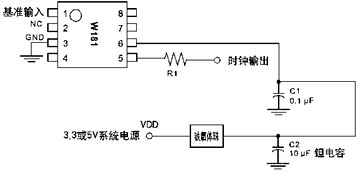

W181-01/02/03有8引脚SOIC封装及14引脚TSSOP封装,及其典型应用电路框图和三种封装管脚排列如图1所示。

功能描述

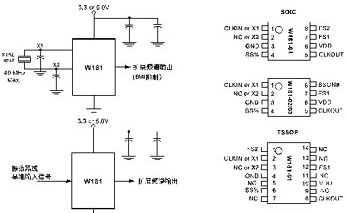

W181采用了频率锁相环(PLL)技术来调制输入时钟,其结果是得到一个输出时钟,它的频率可缓慢地扫过一个接近于输入信号的窄带。基本电路结构如图2所示。

12下一页> 关键字:峰值 EMI W181 本文链接:http://www.cntronics.com/public/art/artinfo/id/80008398

输入基准信号通过分频器除以Q后输入到鉴相器中。来自VCO的信号被反馈分频器除以P后也送到鉴相器中。PLL迫使VCO输出信号的频率发生变化直到被分频后的输出信号和被分频的基准信号在鉴相器的输入端匹配。输出频率等于基准频率的P/Q的比例倍(注意:对于W181,输出频率等于输入频率)。扩展频谱频率时钟发生的独特性在于一个调制波形在输入端经过叠加才进入VCO中,这使得VCO的输出能缓慢扫过预制频带。

输入基准信号通过分频器除以Q后输入到鉴相器中。来自VCO的信号被反馈分频器除以P后也送到鉴相器中。PLL迫使VCO输出信号的频率发生变化直到被分频后的输出信号和被分频的基准信号在鉴相器的输入端匹配。输出频率等于基准频率的P/Q的比例倍(注意:对于W181,输出频率等于输入频率)。扩展频谱频率时钟发生的独特性在于一个调制波形在输入端经过叠加才进入VCO中,这使得VCO的输出能缓慢扫过预制频带。使用SSFTG进行频率选择

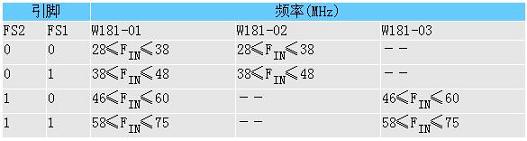

在扩展频谱时钟发生中,EMI减弱要依靠整形、调制率和调制波形的频率。当整形及调制波形的频率由已定的频率来确定时,调制的百分比就会有所不同。使用频率选择位(FS1及FS2)能设置频率范围。扩展率也被设到-1.25%之间。见表2。高扩展率加强了对EMI的减弱,然而,高扩展率却可能会因为超过系统最大额定频率或低于平均频率而使性能受到影响。鉴于上述原因,扩展率多在0.5%--2.5%之间。

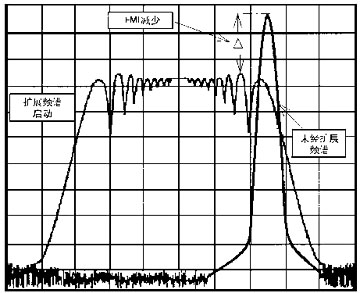

扩展频谱定时信号的发生

使用扩展频谱定时信号发生的好处如图3所示。它表示出了一个时钟谐波EMI的分布。将典型时钟的EMI与Cypress扩展频谱频率定时信号发生的EMI进行比较。请注意典型时钟中的尖峰信号,该尖峰信号使系统的准峰值EMI测试衰退。经过频谱扩展后,峰值能量将极大减少(至少8dB),因为能量通过一个更宽的带宽散发了。

调制波形

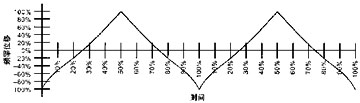

对EMI减弱的调制波形的整形是很关键的。调制的方案用来实现最大减小EMI,如图4所示。调制周期在X轴上以周期长度的百分比为单位。Y轴表示不同的频率值,也是以总扩展频率的百分比为单位。

----Cypress的频率选择表通过两种方法表示了调制百分比,第一种方法是将扩展频带表示成程序控制平均输出频率的百分比,关于程序控制平均频率是对称。这种方法通常见于在频率扩展选择表中使用的公式fcenter±XMOD%。第二种方法是指定最大的工作频率和扩展频带作为其百分比。输出信号从频带的低端扫向最大频率。此方法的表达式为fmax-XMOD%。不论此表达式用在什么时候,都应确保最大频率不会超限。在时钟以最大时钟速度来驱动器件的应用中,这一点是很重要的。

----Cypress的频率选择表通过两种方法表示了调制百分比,第一种方法是将扩展频带表示成程序控制平均输出频率的百分比,关于程序控制平均频率是对称。这种方法通常见于在频率扩展选择表中使用的公式fcenter±XMOD%。第二种方法是指定最大的工作频率和扩展频带作为其百分比。输出信号从频带的低端扫向最大频率。此方法的表达式为fmax-XMOD%。不论此表达式用在什么时候,都应确保最大频率不会超限。在时钟以最大时钟速度来驱动器件的应用中,这一点是很重要的。应用指南

为了在系统应用中发挥最佳性能,应该用如图5所示的电源去耦方案。

VDO去耦对于减少相位抖动和EMI幅射都是很重要的,0.1μF去耦电容的放置应尽可能地接近VDD,否则布线的寄生电感会消去它的去耦能力。图5中的10μF去耦电容应是钽电容。为了更好地实现EMI保护,VDD的接入应穿过一个<上一页12 关键字:峰值 EMI W181 本文链接:http://www.cntronics.com/public/art/artinfo/id/80008398?page=2

VDO去耦对于减少相位抖动和EMI幅射都是很重要的,0.1μF去耦电容的放置应尽可能地接近VDD,否则布线的寄生电感会消去它的去耦能力。图5中的10μF去耦电容应是钽电容。为了更好地实现EMI保护,VDD的接入应穿过一个<上一页12 关键字:峰值 EMI W181 本文链接:http://www.cntronics.com/public/art/artinfo/id/80008398?page=2