高频率应用下的电路保护

中心议题:

- 高速数据线路对保护器件的要求

- PESD器件的特点与应用

- 具有极低电容值的ESD抑制

- POE技术应用于数据线

- 选用适合GDT作为第一级雷击防护

Ethernet这一全球应用最为广泛的局域网技术在不断更新:802.3ae的出现使10Gbps的速率已成为主流厂商研究目标;LAN和WAN的融合使其应用场所已不再局限于室内;POE技术赋予以太网络新的含义。在更高速率的呼声中,USB3.0标准山雨欲来风满楼,新版IEEE1394也来势汹汹。所有这些都使未来数据通讯成为一个高速的世界。

随着行业的汇聚联合,对数据端口传输速率要求的增高,制造商必须对设备需求作出响应,以便容纳更高的数据率以及符合当前和拟议中的通信需求。另外,保护昂贵的设备不会受到因用户错误操作、环境危害或电源变化所引起的致命的损坏也是一项关键的设计课题。

以太网口、USB2.0、IEEE1394、ITV应用和操作中使用的数字式可视接口(DVI)和高清晰度多媒体接口(HDMI)协议允许高速数据传输率,并可以支持即插即用热插拔安装和操作。但这些外部端口很容易受到来自工作环境和周边设备的破坏性的ESD脉冲的伤害。

ESD抑制器件除了保护数据传输线路之外,必须保持其信号的完整性。部分以太网端口由于用于楼宇之间,有遭受雷击感应被损坏的危险,附近电力线的影响也不容忽视。防雷元器件除了保护网络后端的PHY不被击穿之外,也必须保持信号传输中不会掉包。POE技术由于会叠加在信号双绞线上,这给此类过压防护带来新的挑战。

通常,较为流行的用户端以太网联接支持100Mbps的数据传输;USB2.0支持480Mbps的数据传输;DVI和HDMI协议更是分别支持高达8Gbps和5Gbps的数据传输带宽。在Ethernet、USB2.0、DVI和HDMI的高速数据率下,传统保护装置的寄生电容可能破坏信号的完整性或令其失真。失真表现为由较慢的上升和下降时间所致的高态/低态瞬变的前沿和后沿被修圆。

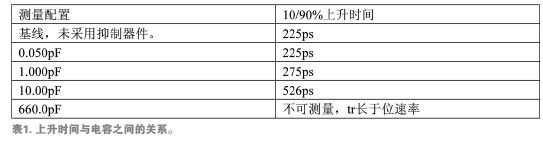

上升和下降时间较慢会给系统带来一些问题,其中最重要的是时序问题。电路在特定的时间需要稳定的“高”态和“低”态。随着各状态之间过渡时间的增加,电路有可能检测到不完整的过渡期,从而将数据误差引入系统。表1是不同寄生电容ESD抑制器件对数据上升沿时间(10%至90%高电平)所造成的影响比较。

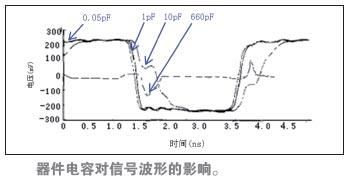

传输速率为12Mbps时,其保持电平的时间要长得多(80ns)。在此数据传输率条件下,1OpF或更小的电容值将使得数据通过时的失真最小。当传输速率提高到480Mbps时,信号具有短得多的电平保持时间(2.0ns)。此时1OpF电容的ESD抑制器件已经引起波形失真:它减少了电平保持时间并使前沿和后沿的形状大为改变。而660pF电容的ESD抑制器件则造成了相当大的失真,以致于波形甚至无法达到信号工作电压。图1显示了不同ESD抑制器件对480Mbps数据波形的影响。

图1.器件电容对信号波形的影响

这些数据揭示了在进行超高速系统的数据传输线路保护时抑制器的电容特性的重要性。尽管现有的各种抑制器均能够提供有效的ESD或雷击保护功能,但不能以牺牲系统的信号完整性为代价。因此,在把抑制器引入电路设计之前,必须对其电容有所考虑。

具有极低电容值的ESD抑制元件(如PESD器件)以及具有极低电容值的雷击解决方案能够在提供保护功能的同时保持高速数据信号的数据完整性。由于传输最高速率的不同,不同的数据接口所能接受的最高电容是不一样的。