以太网端口保护的智能化方案

中心议题:

- 爬电距离和PCB走线间隙

- 雷击引起的浪涌、静电放电、电快速瞬变和电缆放电事件

- 保护器件的电路连接

- 以太网端口保护器件选型参数

除了合适的器件爬电距离和电气走线间隙之外,良好的以太网端口设计实践还需要过压和过流保护器件。算出印制电路板(PCB)的爬电距离和电气间隙之后,我们必须为以太网I/O连接的两端都选择保护器件,即线路(RJ-45)侧和驱动器(物理层或PHY)侧。本文用以太网保护器件最常用的多通道瞬态电压抑制器(TVS)二极管阵列为例介绍以太网端口保护的智能化方案。

以太网保护器件一般是多通道瞬态电压抑制器(TVS)二极管阵列,在各种保护技术中,这种阵列可以提供最低的箝位电压。它们提供了各种各样的小形封装,从用于单端口保护的单个器件到保护多条线路的多个器件。这些器件全部整合在一个封装内,从而最大限度降低了对电路板的空间要求。

TVS二极管阵列在以下情况下使用:被保护的PHY电路需要低箝位电压、典型值为0.4pF至5pF的低电容以及0.1μA至25μA的低漏电流;必须对多条线路提供保护并且电路板空间有限时;由于各种威胁因素而出现瞬态电压时。

必须为以下四种主要的过压电气威胁选择具有合适特性的TVS二极管阵列:雷击引起的浪涌、静电放电(ESD)、电快速瞬变(EFT)和电缆放电事件(CDE)。低电容在这些器件中尤其重要,它可以避免信号失真,特别是在吉比特以太网电路中。

TVS二极管阵列必须连接在一起,以确保能够充分地抑制这些威胁因素。根据实际情况,它们应尽可能靠近电气威胁的进入点,同时将相同的地参考作为要保护的PHY.

威胁抑制可能需要考虑其他的设计因素,比如使用保险丝,将电源线旁路电容接地(靠近PHY电源输入引脚),以确保实现正常的电源滤波。应根据IEC或其他相关标准对PCB原型进行测试,以验证PCB布局是否具有合适的爬电距离和电气间隙。这在出现电力故障和浪涌情况时,有助于防止电弧形成,并使TVS二极管阵列能够有效地抑制这些事件的发生。

爬电距离和PCB走线间隙

为了防止以太网PCB上出现介电击穿和火花,线路侧和地应设置足够的爬电距离和走线间隙。爬电距离是两个导电部件之间或者一个导电部件与设备的边界面之间沿绝缘体表面所测得的最短路径。

足够的爬电距离可以防止漏电起痕,该过程会在绝缘材料表面产生局部衰减的部分传导通路,从而在绝缘表面或附近产生放电。

漏电起痕的程度取决于两大因素:PCB材料的相对漏电起痕指数(CTI)以及诸如高度、湿度和污染物等环境因素。CTI指标提供了在标准测试时由于漏电起痕引起故障的电压的数值。IEC 112标准给出了漏电起痕和CTI的全面说明。

电气间隙是两个导电部件(比如电路板走线)之间或者导电部件与设备的边界面之间在空中测得的最短距离。电气间隙有助于防止部件之间由于空气电离而产生的介电击穿。介电击穿水平还受PCB CTI等级、工作环境的相对湿度、温度和污染程度的影响。

板级设计人员经常会在计算爬电距离和电气间隙时考虑峰值工作电压,不过还需要考虑电气瞬态过程。有些瞬态电压甚至高达几千伏。

实验室测试表明,要耐受2kV的瞬态电压,FR4电路板走线间距应至少为25mil.不过,对于标准以太网双绞线为5mil、走线宽度为5mil的以太网板布局,该电气间隙可能太大了。

这是瞬态保护的另一个重要原因:降低高压使间距可以更小,即高压会由于TVS二极管阵列的箝位作用而得到抑制。在UL 60950-1标准中,表2K表明,2.8kV的最小电气间隙为8.4mm(330mil),1.4kV的最小电气间隙为6.4mm(252mil)。不过这针对的是稳态电压,而不是针对发生浪涌时快速上升的dv/dt.因此,通过TVS保持走线之间的电势差对于电路板布局来说至关重要。

了解瞬态事件的特性和极性有助于指导设计人员开发出最好的以太网端口保护方案。有了这种理解之后,就可以很好地把握如何定位和连接保护器件。

雷击引起的浪涌

大多数标准、建议或法规都将共模(纵向)浪涌要求界定为最低抗扰度级别。这些共模事件可以转换成差分(金属)事件。因此,有些标准、建议和法规还可以定义差分浪涌要求抗扰度级别。GR-1089-Issue 6,2 IEC 61000-4-5和ITU K20/21对波形的产生和测试过程有所介绍。

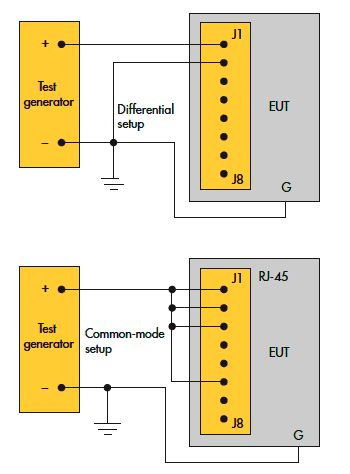

图1显示了这两种案例的测试装置。在差分模式下,两个导体或引脚(即J1和J2)连接在测试设备的正负两端,因此在RJ-45端口处插入的浪涌事件仅出现在这两个导体之间。大部分能量都在图2所示的线路侧保护装置TVS1(x2)中耗费。不过,有些能量也会通过变压器耦合,在变压器的驱动器侧产生共模或差分事件。

图1:在差分测试中,两个导体或引脚连接测试设备的正负两端。

下页内容:静电放电、电快速瞬变和电缆放电事件