信号源的使用方法

中心议题:

- 探讨信号源的使用方法

- 了解信号发生方法

在电子测试和测量中,经常要求信号源,生成只有在外部提供时才会有的信号。信号源可以提供“已知良好”的信号,或者在其提供的信号中添加可重复的数量和类型已知的失真(或误码)。这是信号源最大的特点之一,因为仅使用电路本身,通常不可能恰好在需要的时间和地点创建可预测的失真。从设计检验到检定,从极限和余量测试到一致性测试,信号源可以用于数百种应用。

因此,有多种信号源结构可供选择也就不足为奇了,而每种结构都有各自的优点、功能和经济性,适用于特定的用途。在本文中,我们将比较两种信号发生结构:一种用于任意波形/ 函数发生器中,一种用于任意波形发生器中。选择结果在很大程度上取决于应用。

了解信号发生方法

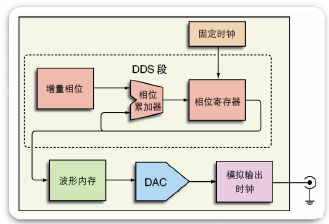

任意波形/ 函数发生器(AFG)通过读取内存的内容,来同时创建函数波形和任意波形。大多数现代AFG 采用直接信号合成(DDS)技术,在广泛的频率范围上提供信号。

任意波形发生器(AWG)基于真正可变时钟结构(通常称为" 真正的arbs*1"),适用于在所有频率上生成比较复杂的波形。AWG 也读取内存的内容,但其读取方式不同(后面进行了介绍)。处理先进通信和计算单元的设计人员选择AWG,驱动采用复杂调制和带有异常事件的高速信号。结果,AWG 占据了研究、开发和工程应用的最高层。

这两种结构在波形生成方法上有着很大差异。本技术简

介讨论了基于可变时钟的任意波形发生器和基于DDS的任意波形/ 函数发生器之间的差别。

透过前面板:比较两个平台

AWG:概念简单,灵活性最大

尽管AWG 在这两种结构中更加灵活,但AWG 的底层波形生成技术非常简明。AWG的播放方案可以视为“反向取样”。这是什么意思呢?看一下信号取样平台-- 示波器,它通过在连续时点上数字化模拟信号的电压值,来采集波形,其取样频率取决于用户选择的时钟速率。得到的样点存储在内存中。

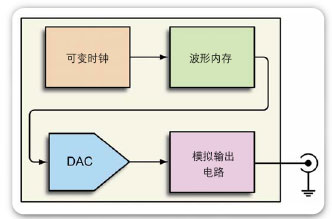

AWG的流程相反。AWG开始时波形已经在内存中。波形占用指定数量的内存位置。在每个时钟周期中,仪器从内存中输出另一个波形样点。由于代表波形的样点数量是固定的,因此时钟速率越快,读取内存中波形数据点的速度越快,输出频率越高。换句话说,输出信号频率完全取决于时钟频率和内存中的波形样点数量*2。图1 中简化的方框图概括了AWG 结构。

AWG 的灵活性源自其内存中存储的波形。波形可以采取任何形状;它可以有任意数量的畸变,或根本没有畸变。在基于PC 的工具的帮助下,用户可以开发人们想得到的几乎任何波形(在物理限制内!)。可以在仪器能够生成的任何时钟频率上,从内存中读取样点。不管时钟是以1 MHz运行还是以1 GHz运行,波形的形状相同。

*1 工程师通常使用"arb" 来指任何类型的任意波形发生器。

*2 当然任何AWG 型号都有最大内存容量。波形占用的深度可能要小于全部容量。

AFG 在高频中采取高效的快捷方式

AFG也使用存储的波形,作为输出信号的基础。其样点读数中涉及时钟信号,但结果类似。

AFG 的时钟以某个固定速率运行。由于波形样点的数量在内存中也是固定的,因此AFG 怎样才能在变动频率上提供波形呢?例如,想象一下您正在使用一部AFG,它存储由1000 个样点组成的波形,以1 MHz 的固定速率输出。输出信号的周期将恰好固定在1 ms (1kHz)。很明显,单频信号源在大多数应用中用途有限。因此,DDS 技术提供了一个解决方案。基于DDS的仪器不读取每个样点,而是读取不到1000 个样点,来重建波形。

如前所述,AFG保持固定的系统时钟频率。360度时钟周期分布在所有波形样点中,DDS 段根据波形长度及用户选择的频率自动确定相位增量。

高频设置会导致大的相位增量,使AFG 在通过360 度周期时迅速向前跳,提供高频信号。低频值导致小的增量,触发相位累加器以较低的步长步进通过波形样点,甚至会重复各个样点,构成360度,生成频率较低的波形。

这一决策背后的数学运算超出了本文的讨论范畴。可以这样讲,AFG根据自己的内部算法跳过选择的波形数据点。由于相位增量方法,它并不是在每个周期中一直跳过相同的样点数。AFG为生成变化的波形和频率提供了一种快捷方式,但最终用户不能控制跳过哪些数据点。

这必然对输出波形保真度造成一定的影响。具有连续形状的波形(正弦、三角形等等)通常不是问题,但可能会影响当前数字环境中常见的带有快速转换的信号,如脉冲和瞬变。例如,假设在新的电信交换机元件上进行极限测试。测试波形是一串二进制脉冲,其中一个脉冲在上升沿上有一个瞬变。在某些频率上,DDS相位增量可能会刚好跳过瞬变,而不会作为信号的一部分在时钟中输出瞬变。对被测器件(DUT),信号类似于没有干扰的脉冲流,由于缺少任何实际“极限”,这种极限测试是无效的。

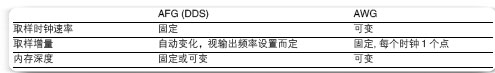

表1. AFG 与AWG 取样特点比较

AFG结构的实现成本要低于全功能AWG工具集。结果,它非常经济,可以供各个工程师和科研人员使用。此外,AFG拥有某些独有的性能优势。部分领先型号拥有任何波形发生平台中最优秀的频率捷变性,即能够在不同频率之间平滑切换,而不会在信号中产生不连续点。

表1 概括了AFG 平台和AWG 平台的时钟和内存特点。

深入细节

为更好地比较AWG和AFG结构,我们将进行简单的“案例分析”。我们将考察这两个平台处理定义输出波形的样点的方式。

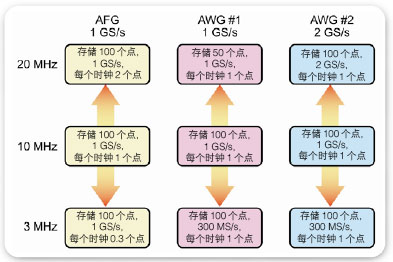

这一比较涉及三种仪器:最大取样速率1 GS/s的AFG;最大取样速率1 GS/s的AWG #1;最大取样速率2 GS/s 的AWG #2。

我们的目标是在3 MHz - 20 MHz 的频率范围内生成一个正弦波。这两台AWG和AFG都在100点的取样内存中装有一个正弦波周期。图3显示了这三个平台的特点怎样影响其任务处理方式。

这三种工具都以1 GS/s 的取样速率读取100 个点,生成10 MHz 正弦波(图3 中的中间行):

图3. T 管理输出信号频率的三种方法。

AFG 的DDS 单元收到命令,在输出上提供10 MHz,它计算出1 GS/s 时钟每摆动一下增加1 个点。它接触到100 个样点中的每个点。

两个AWG中的时钟都被手动设置为1 GS/s,它们也读取100 个点,生成10 MHz 波形。

在把输出频率设为3 MHz (底部行),其方法出现分歧:

AFG 的时钟仍以1 GS/s 的固定速率运行。但现在,DDS把增量自动设成时钟每摆动一下0.3个点;也就是说,各个数据点重复三次或四次。

两个AWG中的时钟频率必须手动降到300 MS/s。时钟现在更慢地读过样点,生成3 MHz 的输出频率。

现在,输出频率必须提高到20 MHz。这三个平台以不同方式迎接这一挑战:

AFG 的DDS 单元把取样增量设为两个样点。它每隔一个样点读取一个样点,共使用50个点定义波形。其长度只是读取100个点的一半。结果是一个20 MHz输出信号。

与所有AWG 在任何频率设置上一样,AWG #1 时钟每摆动一下读取一个样点。但是,由于其最大取样速率是1 GS/s,因此它不能在50 ns 的20 MHz 正弦波周期中读取100个点。因此,必须通过用户故意干预,把存储的波形图像下降到总共50 个点。结果是一个20 MHz 输出信号。

它提供了多种软件工具,在要求时帮助用户编辑样点数量,某些仪器为此提供了内置功能。在使用外部工具时,必须把修改后的波形重装到AWG 中。

AWG #2时钟每摆动一次读取一个样点,但时钟速率翻了一倍,提高到2 GS/s。仪器读取100 点内存的速度提高了一倍。结果是一个20 MHz 输出信号。

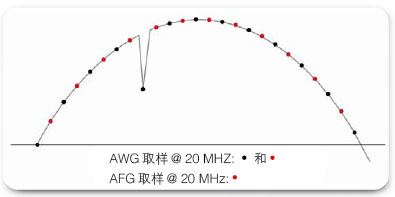

乍一看,似乎AWG #1限于与AFG相同的波形分辨率,但有一个关键区别。在20 MHz的输出频率上,AWG读取正弦波中50 个点的每个点。AFG 跳过样点。

图4. AFG 跳过样点,提高其输出频率。在某些频率上,可以忽略各个信号细节。

AWG读取每个点(红色或黑色),而不管输出频率的设置是多少。如果输出频率设为10 MHz,AWG 读取25 个点。如果设为20 MHz,AWG仍读取25个点。如果AWG内部的最大时钟速率没有足够高,通过读取所有样点来生成希望的频率,那么可以降低点数。假设用户在削减AWG 的样点数量时保留希望的波形特点,仪器将在每个周期中可靠地提供一个毛刺。

现在看一下AFG。如果输出频率设为10 MHz,它读取每个点。如果设为20 MHz,它会每隔第二个点读取一个点。这些DDS 点用红色显示。注意,AFG 完全绕过毛刺。它刚好跳过定义跌落的那个样点。波形输出为一个清楚的正弦波。被测器件没有收到畸变。

包括畸变的信号

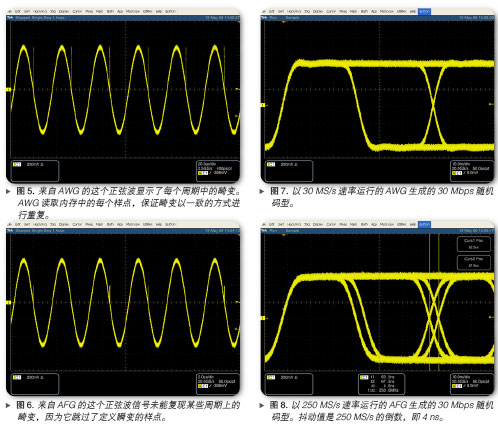

图4是严格的“教科书”实例。根据涉及的算法和频率,DDS 将选择要跳过的不同点,因此红色样点和黑色样点之间的二分法并不适用于任何情况。图5和图6是实际屏幕图,它们突出显示了两种取样和波形重建结构的差别。

生成伪随机码流(PRBS)码型

在使用基于DDS的AFG及固定取样速率生成伪随机码流(PRBS)码型时,抖动是一个问题。简单地说,AFG一般对快速变化的脉冲上升沿和下降沿应用相当于抖动的一个相同周期*3。例如,如果AFG的取样速率是250MS/s,那么信号边沿上将出现4 ns 的抖动。抖动值与AFG 的取样周期相同。

之所以出现抖动,是因为AFG拥有固定的取样速率,其不是数据速率的倍数。AWG则没有这种限制(尽管任何实际环境信号源都会产生某些抖动)。

优点/ 缺点

工具的最终选择总是取决于应用。用户总是面临着“好大喜功”的问题,这在取样速率和内存深度中意味着最大的数字。而聪明的用户则会根据应用的实际信号要求来作出选择。

例如,某些中档AFG 提供了1 GS/s 的取样速率,某些同类AWG 则只提供了600 MS/s 的取样速率。但当应用要求在广泛的频率范围上可靠地提供小信号细节时,最好选择AWG,因为AWG 读取存储的波形上的每个样点,可以保证准确地复现瞬变、边沿上升时间、甚至噪声效应。

此外,AWG 还适合为低抖动数字波形提供信号,如伪随机码流(PRBS)。这使其成为许多串行总线测试应用的最佳解决方案。

AWG 不可避免也有一些缺点。如前面所述的AWG#1,编辑样点数、以提高输出频率不象AFG改变一个设置、进而改变频率那样方便。

由于AWG结构在所有通道中依赖一个可变主时钟,因此在多条通道中同时生成不同频率要求在每条通道后面存储一个不同的波形文件。

例如,如果需要从通道1 中生成一个10 MHz 正弦波,同时从通道2 中生成一个20 MHz 正弦波,那么通道2的波形内存必须加载两个周期。所以,在时钟步进通过内存时,对通道1 中的每一个周期,通道2 中会出现两个周期,使输出频率翻一番。当不同频率不是基本频率的倍数时,这一过程会变得更加复杂。

AFG提供了一套不同的优势。其相噪指标和频率捷变一般要优于AWG。在某些领先的AFG 型号中,每条通道中的DDS单元独立操纵主时钟,从而可以简便地一次提供多个频率。此外,AFG通常是各种选项中最经济的解决方案。任意函数发生器已经成为通用信号源的支柱。

AFG不太适合要求低抖动和非常窄的瞬变的应用。该平台不适合PRBS应用,因为其输出波形本身的抖动较高,会导致DUT接收单元发出错误响应。对要求可预测的信号失真的极限测试,AFG跳过样点的技术会在某些频率上产生误导结果。

总结

通常情况下,选择AFG还是AWG 主要是取决于哪种方法最适合具体应用:

在应用要求干净规则的波形时,或要求从一个频率到另一个频率快速切换,或在多条通道中必须同时提供不同频率时,应选择AFG。

对最复杂的信号应选择AWG,如PRBS 流、调制的RF 信号等等。当信号源必须在提供的每个频率上在每个工作周期中可靠地生成畸变、受控抖动和噪声时,更适合采用AWG。