igbt的四种失效模式分析

摘要:本文通过案例和实验,概述了四种IGBT及其子器件的失效模式:MOS栅击穿、IGBT-MOS阈值电压漂移、IGBT有限次连续短路脉冲冲击的积累损伤和静电保护用高压npn管的硅熔融。

关键词:栅击穿 阈值电压漂移 积累损伤 硅熔融

1、 引言

IGBT及其派生器件,例如:IGCT,是MOS和双极集成的混合型半导体功率器件。因此,IGBT的失效模式,既有其子器件MOS和双极的特有失效模式,还有混合型特有的失效模式。MOS是静电极敏感器件,因此,IGBT也是静电极敏感型器件,其子器件还应包括静电放电(SED)防护器件。据报道,失效的半导体器件中,由静电放电及相关原因引起的失效,占很大的比例。例如:汽车行业由于失效而要求退货的器件中,其中由静电放电引起的失效就占约30%。

本文通过案例和实验,概述IGBT及其子器件的四种失效模式:

(1) MOS栅击穿;

(2) IGBT——MOS阈值电压漂移;

(3) IGBT寿命期内有限次连续短路脉冲冲击的累积损伤;

(4) 静电放电保护用高压npn管的硅熔融。

2、 MOS栅击穿

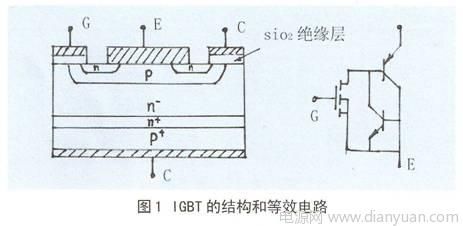

IGBT器件的剖面和等效电路见图1。

由图1可见,IGBT是由一个MOS和一个npnp四层结构集成的器件。而MOS是金属—氧化物—半导体场效应管的简称。其中,氧化物通常是硅衬底上氧化而生成的SIO2,有时还迭加其他的氧化物层,例如Si3N4,Al2O3。通常设计这层SiO2的厚度ts:

微电子系统:ts<1000A电力电子系统:ts≥1000A。

SiO2,介质的击穿电压是1×1019V/m。那么,MOS栅极的击穿电压是100V左右。

人体产生的静电强度U:

湿度:10-20%,U>18000V;60-90%时,U≥1500V。

上述数据表明,不附加静电保护的MOS管和MOS集成电路(IC),只要带静电的人体接触它,MOS的绝缘栅就一定被击穿。

案例:上世纪六十年代后期,某研究所研制的MOS管和MOS集成电路。不管是安装在印刷电路板上还是存放在盒中的此种器件,都出现莫名其妙的失效。因此,给MOS一个绰号:摸死管。

如果这种“摸死”问题不解决,我国第一台具有自主知识产权的MOS集成电路微型计算机就不可能在1969年诞生。经过一段时间的困惑,开始怀疑静电放电的作用。为了验证,准备了10支栅极无任何防护的MOS管,用晶体管特性测试仪重新测试合格后,即时将该器件再往自己身上摩擦一下再测特性,结果发现:100%栅击穿!随后,在MOS管的栅极一源极之间反并联一个二极管,问题就基本解决。意外的结果:“摸死管”成了一句引以为戒的警语。该研究所内接触和应用MOS管MOS-IC的同事,对静电放电对器件的破坏性影响都有了深刻的体验。

3、 IGBT——MOS阈值电压漂移——一种可能隐藏的失效模式

MOS管的阈值电压Vth的方程式:

(1)式中VSS=表面态阈值电压,Vhh =本征阈值电压,常数(费米势),N=硅衬底杂质浓度。

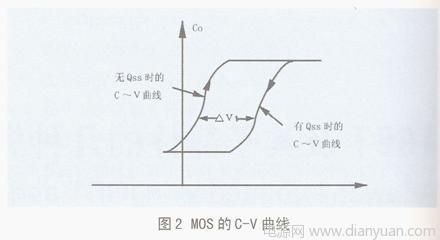

图2是栅电压VG和栅电容CO的C—V曲线,曲线上的箭头表时扫描方向。

由图2可见。C—V曲线是一条迟滞回路,该回路包络的面积等于表面态电荷,QSS是由Si—SiO2界面缺陷和正电荷离子引起的。而且,Si—SiO2界面的QSS始终是正的。即VSS总是向VITH正向移动。这就决定了沟增强型MOS管和P沟数字集成电路容易实现。

为了减小QSS和防止SiO2——Si界面电荷交换与移动,引起阈值电压漂移,采取了许多措施:

(1) 将<111>硅衬底换为<100>硅衬底,减小硅表面的非饱和键;

(2) 制备工艺中使用的石英器皿,气体和化学试剂均提升纯度级别,尽量减小Na离子的污染含量;

(3) 研发新的绝缘栅介质系列:

·Si3N4——Si,Si3N4——SiO2——Si;

·Al2O3——Si,Al2O3——SiO2——Si。

以上措施,对低压微功耗的微电子的应用,已证明MOS与MOSIC是可靠的。但是对于电力电子应用的场合:高电压,大电流和工作温度范围较宽。特别是,静电放电电压接近栅极击穿电压而又未穿栅极时,例如上文所示接近100V时,仍有隐忧:

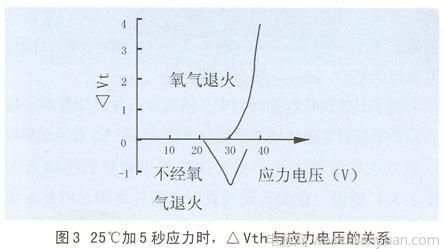

(1) 较高栅电压下,阈值电压漂移较大,图3示出P沟硅栅MOS在高栅电压下的。由图3可见,栅电压VG=40V时,=4V。

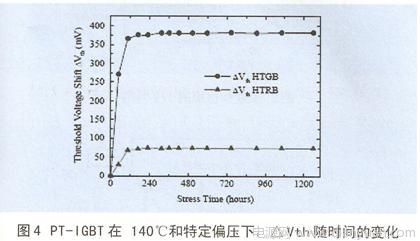

(2) PT—IGBT在高温栅偏压下阈值电压漂移。图4给出PT—IGBT(IRG4BC20F)在(1)栅已射极Gge=20V,Vce=OV(HTGB)和(2)Vge=0V,Vce=0.8V(HTRB)在140℃,经过1200小时的应力试验结果。由图4中的HTGB曲线可见,栅偏置试验开始后100小时内,时线性增加,随后趋于稳定。

(3) 电可擦只读存贮器(electrically erasable read-only memory,简称EEROM)的存贮单元是氮化硅(Si3N4)—二氧化硅(SiO2)构成的双层绝缘栅的MOS管,它利用栅极注入电荷来改变ROM存贮单元的状态。

(4) MOS是一种单极,多数载流子器件,按半导体器件理论,它的抗辐射,主要是抗γ射线的能力应该比双极、少数载流子器件强,但是,实际情况刚相反。这说明MOS的绝缘栅结构在辐射场下有较大的损伤和电荷交换。

(5) 以上4种情况说明,MOS阈值电压漂移在电力电子的应用条件,即高电压(接近栅击穿电压)、大电流和高温(接近pn结临界温度150℃)时,是一种导致器件和电路失效的潜在参数,似乎仍需系统考察和修订老化条件。所以,将称作是一种可能隐藏的失效模式。

4、 IGBT寿命期限内,有限次数短路脉冲冲击的累积损伤失效

在寿命期限内,IGBT会遇到在短路、雪崩等恶劣条件下工作,它能承受短路脉冲冲击的次数是有限的,并和相关条件有关。

4.1非穿通型(NPT)IGBT的鲁棒性

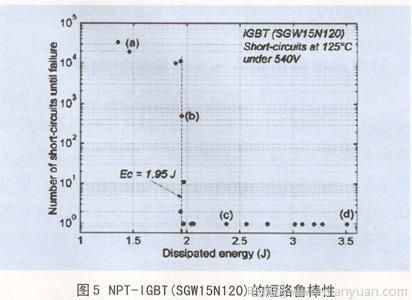

NPT—IGBT的鲁棒性见图5,被测器件是SGW15N120。在540V 125℃时测试。X轴是耗散的能量。Y轴是器件直至损坏的短路周期次数。

由图5可见,在给定条件下,器件有一个临界能量:

EC=V·I·TSC=1.95J(焦耳)

式中,TSC是短路持续时间

当E>EC时,,第一次短路就使器件失效。

当E<EC时,大约要经历104次短路以上,器件会因周期性的能量累积退化使它失效。

当E=EC时,器件失效模式不明确。当能量等于或稍等于EC时,器件关断后,器件的拖尾电流,经过一段延迟时间td f ,将导致热击穿。这段延缓性失效时间为微秒级。

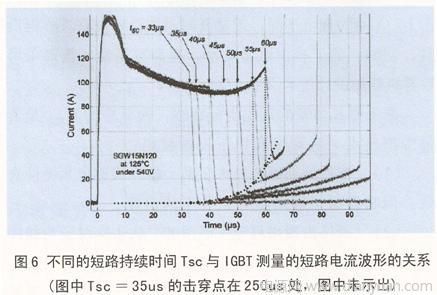

图6给出不同短路续时间TSC,IGBT测量的短路电流波形。

由图6可以看出:

(1) 紧随器件关断后,初始拖尾电流电平(lio)直至失效的延迟时间是由能量决定的,或者说由器件关断后的温度决定的。能量越大,拖尾电流电平也越高,失效的延迟时间则越短。例如,图中给出的最大能量是Tsc=60us,这时,Tds趋向一个极小值。

(2) 当Tsc=33us时,属于E<EC状态,不发生延迟失效。

当Tsc=35us,Tds=25us,开始出现热击穿。

4.2管壳温度的影响

管壳温度对临界能量EC的影响最大,管壳温度升高,EC就下降,测量SGW15N60的结果是:

温度:25℃125℃

EC:0.81J0.62J

4.3集电极电压的影响

集电极电压升高,EC就下降:

VC:250V540V

EC:2.12J1.95J

4.4穿通型(PI)IGBT

PT—IGBT的短路失效特性和NPT—IGBT类似,但是,临界能理值EC比NPT—IGBT低。例如:在125℃,短路电

Vsc=400V时:

600V PT—IGBT(IRGP20u):EC=0.37J

600V NPT—IGBT(SGW15N60):EC=0.62J

4.5结果

(1)每次短路周期耗散的能量E小于由被测电路电压Vce、短路持续时间Tsc和管壳温度决定的临界能量Ec时,IGBT可以连续承受104次以上短路冲击才失效。

(2)在可比的条件下,当E>EC时,一次短路就失效。

(3)NPT—IGBT比PT—IGBT能承受较大的能量冲击。

5、静电放电保护用高压NPN管的硅熔融

在失效的硅器件表面,常常观察到硅熔融,而导致硅熔融的原因却不只一个。例如:器件短路和开关时的瞬间大电流,正向工作区域或热工作区出现二次击穿损伤等到。因此要对静电敏感的器件和电路的输入/输出(I/O)端增设静电放电(ESD)保护装置。而ESD保护装置的器件的硅熔融,也是使被保护的器件和电路失效的原因之一。在本文引言中曾提到汽车应用的器件,其中原因失效要退货的数量中,有30%的失效与ESD有关。由于I/O端的规范不同,需要及时对器件和电路进行再设计。同时,为了减少试验成本,提高可靠性,需要采用计算机辅助设计技术(TCAD)。

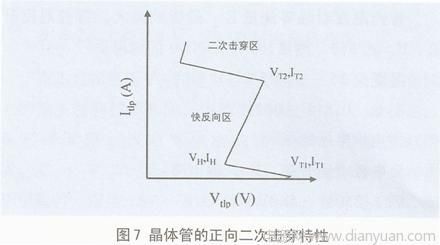

图7是晶体管的正向击穿特性,图7中的VT·是器件的损伤点,其定义有以下三种设定:

(1) 器件的漏泄电流大于某一临界值即定为器件失效。但它忽略了硅熔融和氧化层的击穿;

(2) 器件出现强烈电压崩溃的二次击穿时定为器件失效,但有时器件达到大电流范围也不出现二次击穿。

(3) 当器件的载流子碰撞电离Gi等于肖克莱—里德—霍尔(Shockley—Read—Hall)复合率,同时,总电流随电压反向增加时定为器件失效。

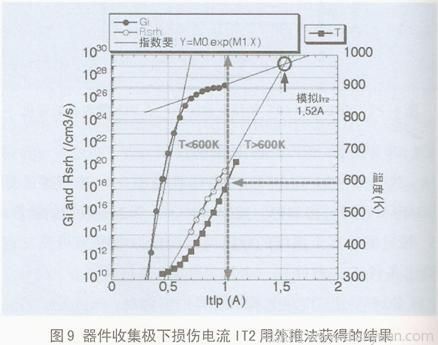

为了验证第(3)种假设,予测二次击穿管点,用0.35um特征尺寸的功率集成电路工艺设计了ESD防护用的标准高压NPN管,并将基极—发射极接地。

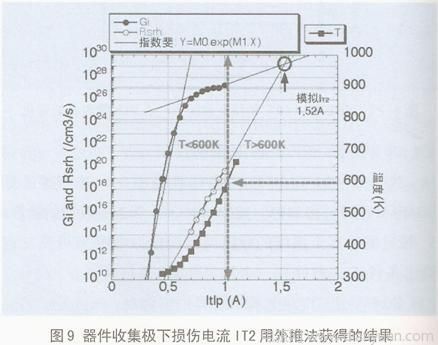

图8是NPN管测量的和用(2)假定来模拟的I-V特性。由图8可见,测量的损伤电流IT2=1.5A,而模拟值是1..8A,有较大误差。图9是用(3)假设外推的结果。其模拟值是1.52A,相当一致。

图10是1A电流应力下,模拟显示该器件有两个热点。一个在收集极触点下,损伤电流IT2=1.52A;另一个热点在发射极之下,用外推法算出的损伤电流远大于2A。所以,首先出现导致失效的硅熔融点应在收集极。图11是该器件失效照片。证明此结果。

本案例说明:

(1)ESD防护器件的失效也是实际器件和电路失效的一种模式。

(2)防护用的NPN管的损伤点可以用TCAD获得。