增强电机控制编码器应用的通信可靠性和性能

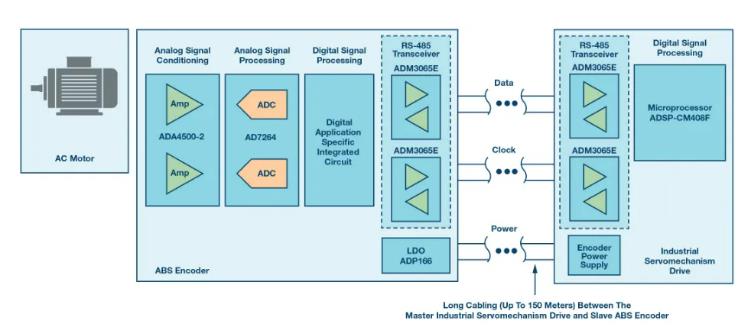

【导读】旋转编码器广泛用于工业自动化系统中。此类编码器的典型应用是电力机械,其中编码器连接到旋转轴,从而向控制系统提供反馈。虽然编码器的主要用途是角度位置和速度测量,但系统诊断和参数配置等其他特性也很常见。图1显示了一个电机控制信号链,其利用RS-485收发器和微处理器连接绝对编码器(ABS编码器)从机和工业伺服驱动器主机,以实现对交流电机的闭环控制。

伺服驱动器和ABS编码器之间的RS-485通信链路通常要求高达16 MHz的高数据速率和低传播延迟时序规格。RS-485线缆延伸长度最大值通常是50米,但有时候也可能长达150米。对数据通信而言,电机控制编码器应用是具有挑战性的环境,因为电气噪声和长电缆会影响RS-485信号传输的完整性。本文重点阐述电机控制应用采用ADI公司50 Mbps (25 MHz)ADM3065E RS-485收发器和 ADSP-CM40x 混合信号控制处理器的主要好处。

图1. 利用RS-485连接绝对编码器从机和伺服驱动器主机,实现对交流电机的闭环控制。

ADM3065E RS-485收发器设计用于在电机控制编码器之类恶劣环境中可靠地工作,并且具备增强的抗扰度和(IEC)61000-4-2 ESD(静电放电)鲁棒性。

01/抗扰度

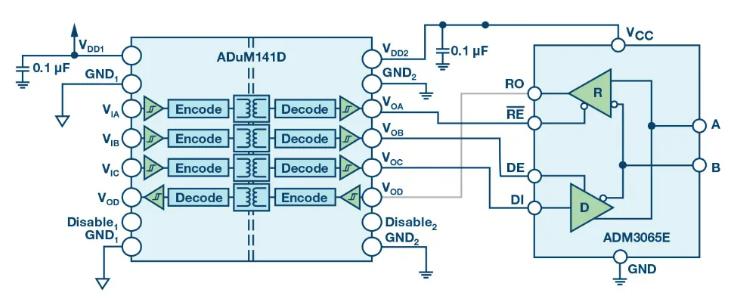

RS-485信号传输是平衡的差分式传输,本身便能抗干扰。系统噪声均等地耦合到RS-485双绞线电缆中的每条导线。一个信号的发射与另一个信号相反,耦合到RS-485总线的电磁场彼此抵消。这降低了系统的电磁干扰(EMI)。此外,ADM3065E增强的2.1 V驱动强度支持在通信中实现更高的信噪比(SNR)。给ADM3065E增加信号隔离可利用 ADuM141D轻松实现。ADuM141D是一款采用ADI公司iCoupler?技术的 四通道数字隔离器。ADuM141D的工作数据速率高可达150 Mbps,因此它适合与50 Mbps ADM3065E RS-485收发器一起工作(参见图2)。直接功率注入(DPI)法测量器件抑制注入到电源或输入引脚的噪声的能力。ADuM141D采用的隔离技术已通过测试,符合DPI IEC 62132-4标准。ADuM141D抗扰度性能超过同类产品。ADuM141D在整个频率范围内保持了出色的性能,而其他隔离产品在200 MHz至700 MHz频段出现位错误。

图2. 信号隔离的50 Mbps RS-485解决方案(简化图,未显示全部连接)。

02/IEC 61000-4-2 ESD性能

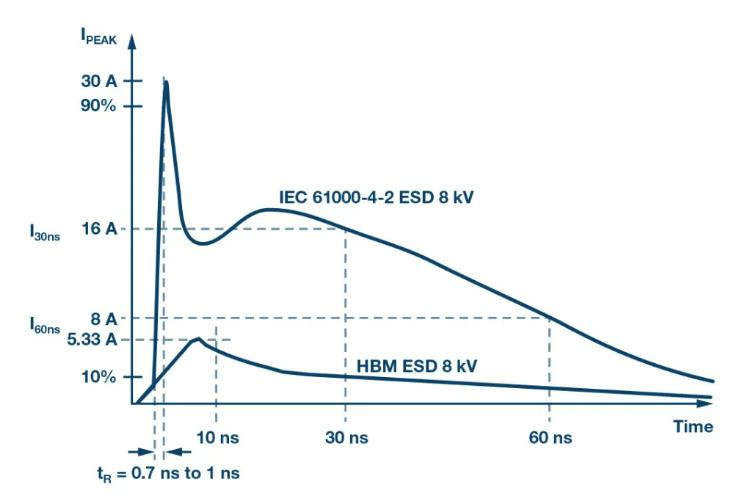

编码器到电机驱动器的裸露RS-485连接器和线缆上的ESD是一个常见系统危险因素。与变速电力驱动系统的EMC抗扰度要求相关的系统级IEC 61800-3标准,要求最低±4 kV(接触)/±8 kV(空气)的IEC 61000-4-2 ESD保护。ADM3065E超过了这一要求,提供±12 kV(接触)/±12 kV(空气)的IEC 61000-4-2 ESD保护。图3所示为IEC 61000-4-2标准中的8 kV接触放电电流波形与人体模型(HBM) ESD 8 kV波形的对比。从图4中可以看出,两个标准规定的波形形状和峰值电流是不同的。与IEC 61000-4-2 8 kV脉冲关联的峰值电流为30 A,相应的HBM ESD峰值电流比该数值的五分之一还小,为5.33A。另一差异为初始电压尖峰的上升时间,对于IEC 61000-4-2 ESD,上升时间为1 ns,相较于与HBM ESD波形关联的10 ns时间要快得多。与IEC ESD波形关联的功率值显著大于HBMESD波形的相应值。HBM ESD标准要求待测设备(EUT)经受3次正放电和3次负放电,而IEC ESD标准则要求10次正放电和10次负放电测试。与标称多种HBM ESD保护级别的其他RS-485收发器相比,具有IEC 61000-4-2 ESD额定值的ADM3065E更适合在恶劣环境中工作。

图3. IEC 61000-4-2 ESD波形(8 kV)与HBM ESD波形(8 kV)的对比

03/EnDat通信协议

编码器使用的通信协议有很多种,例如EnDat、BiSS、HIPERFACE和Tamagawa。尽管有区别,但编码器通信协议在实现方面具有相似点。这些协议的接口是串行双向管道,符合RS-422或RS-485电气规范。虽然硬件层有相同之处,但运行每种协议所需的软件是独一无二的。通信堆栈和所需的应用程序代码均特定于协议。本文主要说明EnDat 2.2接口主机侧的硬件和软件实现。

04/延迟影响

延迟分为两类:第一类是电缆的传输延迟,第二类是收发器的传播延迟。电缆延迟由光速和电缆的电介质常数决定,典型值为6 ns/m至10 ns/m。当总延迟超过半时钟周期时,主机和从机之间的通信就会出故障。对此,设计人员有如下选择:

降低数据速率

减小传播延迟

在主机侧提供延迟补偿

选项3可同时补偿电缆延迟和收发器延迟,因此是确保系统能以高时钟速率通过长电缆运行的有效办法。缺点是延迟补偿会增加系统的复杂性。在延迟补偿不可行的系统中,或在电缆较短的系统中,使用传播延迟短的收发器具有明显的优势。低传播延迟使得时钟速率可以更高,而且不必在系统中引入延迟补偿。

05/主机实现

主机实现包括串行端口和通信堆栈。编码器协议并不兼容标准端口(例如UART),故无法使用大多数通用微控制器上的外设。不过,利用FPGA的可编程逻辑可以在硬件中实现专用通信端口,并支持延迟补偿等高级特性。FPGA方法虽然很灵活,可以针对具体应用进行定制,但也有缺点。与处理器相比,FPGA成本高,功耗大,而且上市时间长。

本文讨论的EnDat接口是在ADI公司的ADSP-CM40x上实现,后者是一款针对电机控制驱动器而开发的处理器。除了脉宽调制器(PWM)定时器、模数转换器(ADC)和sinc滤波器等用于电机控制的外设以外,ADSP-CM40x还有高度灵活的串行端口(SPORT)。

这些SPORT可以仿真多种协议,包括EnDat和BiSS等编码器协议。由于ADSP-CM40x的外设很丰富,所以它不仅能执行高级电机控制,而且能与编码器接口。换言之,无需使用FPGA。

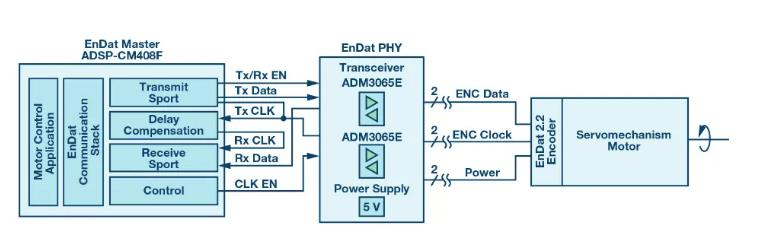

06/测试设置

EnDat 2.2测试设置如图4所示。EnDat从机是Kollmorgen的一款标准伺服电机(AKM22),EnDat编码器(ENC1113)安装在轴上。三对线(数据、时钟和电源线)将编码器连接到收发器板。EnDat PHY上有两个收发器和用于编码器的电源。一个收发器用于时钟,另一个收发器用于数据线路。EnDat主机由ADSP-CM40x结合标准外设和软件而实现。发送端口和接收端口均利用灵活的SPORT实现。

图4. 实验设置

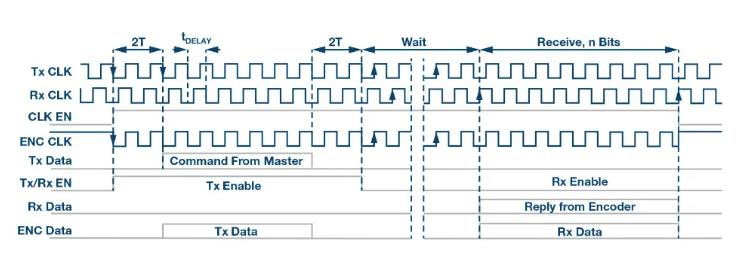

EnDat协议包括多种长度不同的帧,不过这些帧全都基于相同序列,如图5所示。首先,主机发送命令至从机,然后从机处理命令并执行必要的计算。最后,从机将结果送回主机。

图5. EnDat发送/接收序列

发送时钟(Tx CLK)由处理器ADSP-CM40x产生。由于系统延迟,来自编码器的数据在返回处理器之前会与发送时钟错相。为补偿传输延迟tDELAY,处理器还会产生一个接收时钟(Rx CLK),它比发送时钟延迟tDELAY。让接收时钟与自从机收到的数据同相是补偿传输延迟的有效办法。

来自处理器的时钟信号是连续的,而EnDat协议规定,时钟只能在通信期间施加于编码器。在所有其他时候,时钟线路必须保持高电平。为此,处理器产生一个时钟使能信号CLK EN,其被送至ADM3065E数据使能引脚。恰好两个时钟周期(2T)之后,主机开始在Tx DATA上发出命令。

命令有6位长,随后是两个0位。为了控制收发器的数据方向,处理器在传输时将Tx/Rx EN位置1。

在从机准备响应的同时,系统进入等待状态,主机继续施加时钟,但数据线无效。当从机准备就绪时,数据线接收数据被拉高,然后立即发送响应。收到n位响应之后,主机将CLK EN信号设为低电平以停止时钟。与此同时,ENC CLK信号变为高电平。数据流为半双工式, ENC数据图为画在一起的收发数据流。

图6. EnDat数据交换

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

如何从可穿戴设备过渡到医疗设备?

贸泽连续第六年荣获Molex亚太区年度电子目录代理商大奖

实例分享!BMS采样板针对低频磁场抗扰测试解决方案

【测试案例分享】隔离接口芯片失真测试

瑞萨黑科技——高性能AI加速模块DRP-AI