RF ADC为什么有如此多电源轨和电源域?

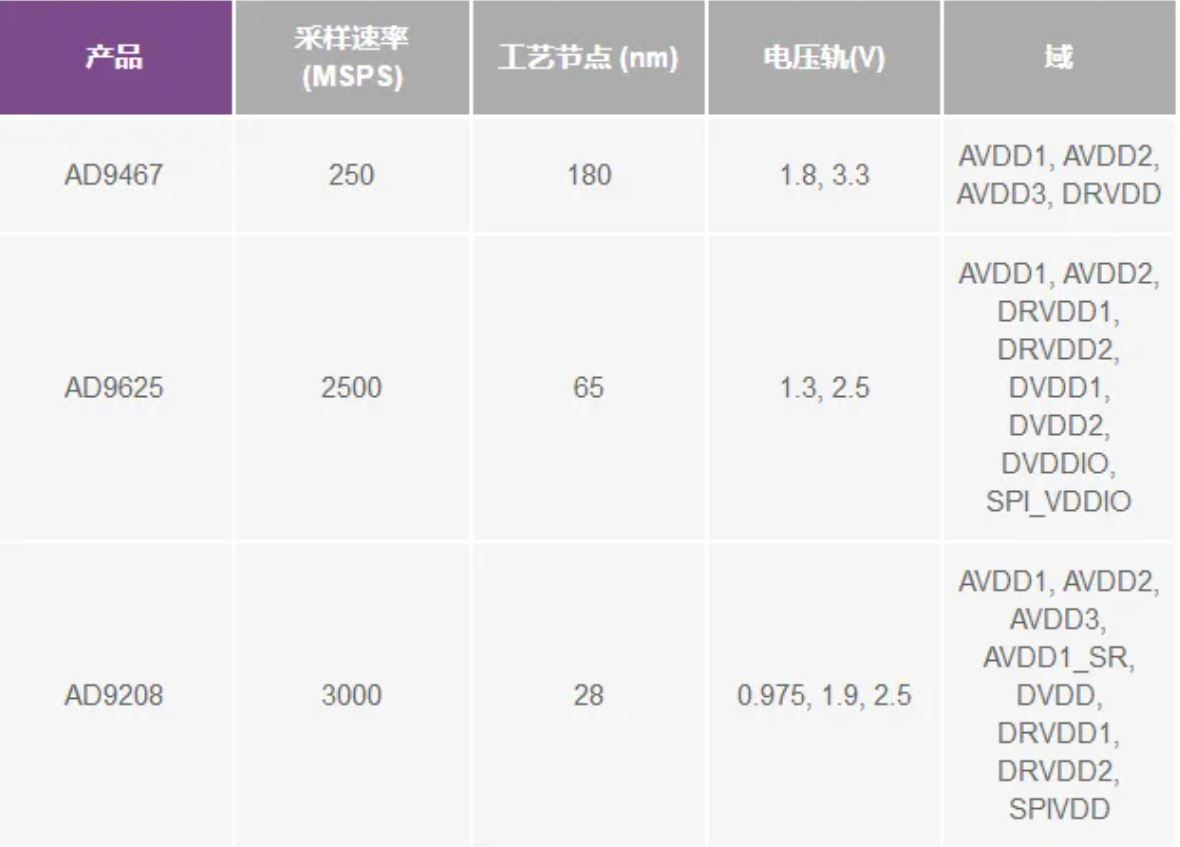

【导读】为了解电源域和电源的增长情况,我们需要追溯ADC的历史脉络。早期ADC采样速度很慢,大约在数十MHz内,而数字内容很少,几乎不存在。电路的数字部分主要涉及如何将数据传输到数字接收逻辑——专用集成电路 (ASIC) 或现场可编程门阵列 (FPGA)。用于制造这些电路的工艺节点几何尺寸较大,约在180 nm或更大。使用单电压轨(1.8 V )和两个不同的域(AVDD和DVDD,分别用于模拟域和数字域),便可获得足够好的性能。

在采样速率和可用带宽方面,当今的射频模数转换器(RF ADC)已有长足的发展,其中还纳入了大量数字处理功能,电源方面的复杂性也有提高。那么,RF ADC为什么有如此多不同的电源轨和电源域?

随着硅处理技术的改进,晶体管的几何尺寸不断减小,意味着每 mm2面积上可以容纳更多的晶体管(即特征)。但是,人们仍然希望 ADC 实现与其前一代器件相同(或更好)的性能。 现在,ADC 的设计采取了多层面方法,其中: 1. 采样速度和模拟带宽必须得到改善; 2. 性能必须与前一代相同或更好; 3. 纳入更多片内数字处理功能来辅助数字接收逻辑。

需要高速度

在 CMOS 技术中,提高速度(带宽)的最普遍方法是让晶体管几何尺寸变小。使用更精细的 CMOS 晶体管可降低寄生效应,从而有助于提高晶体管的速度。晶体管速度越快,则带宽越宽。数字电路的功耗与开关速度有直接关系,与电源电压则是平方关系,如下式所示:

几何尺寸越小,电路设计人员能实现的电路速度就越快,而每MHz每个晶体管的功耗与上一代相同。以 AD9680和 AD9695为例,二者分别采用65 nm和28 nm CMOS技术设计而成。在1.25 GSPS和1.3GSPS时,AD9680和AD9695的功耗分别为3.7 W和1.6 W。这表明,架构大致相同时,采用28 nm工艺制造的电路功耗比采用65 nm工艺制造的相同电路的功耗要低一半。因此,在消耗相同功率的情况下,28 nm工艺电路的运行速度可以是65 nm工艺电路的一倍。AD9208很好地说明了这一点。

裕量最重要

表1:产品比较

隔离是关键

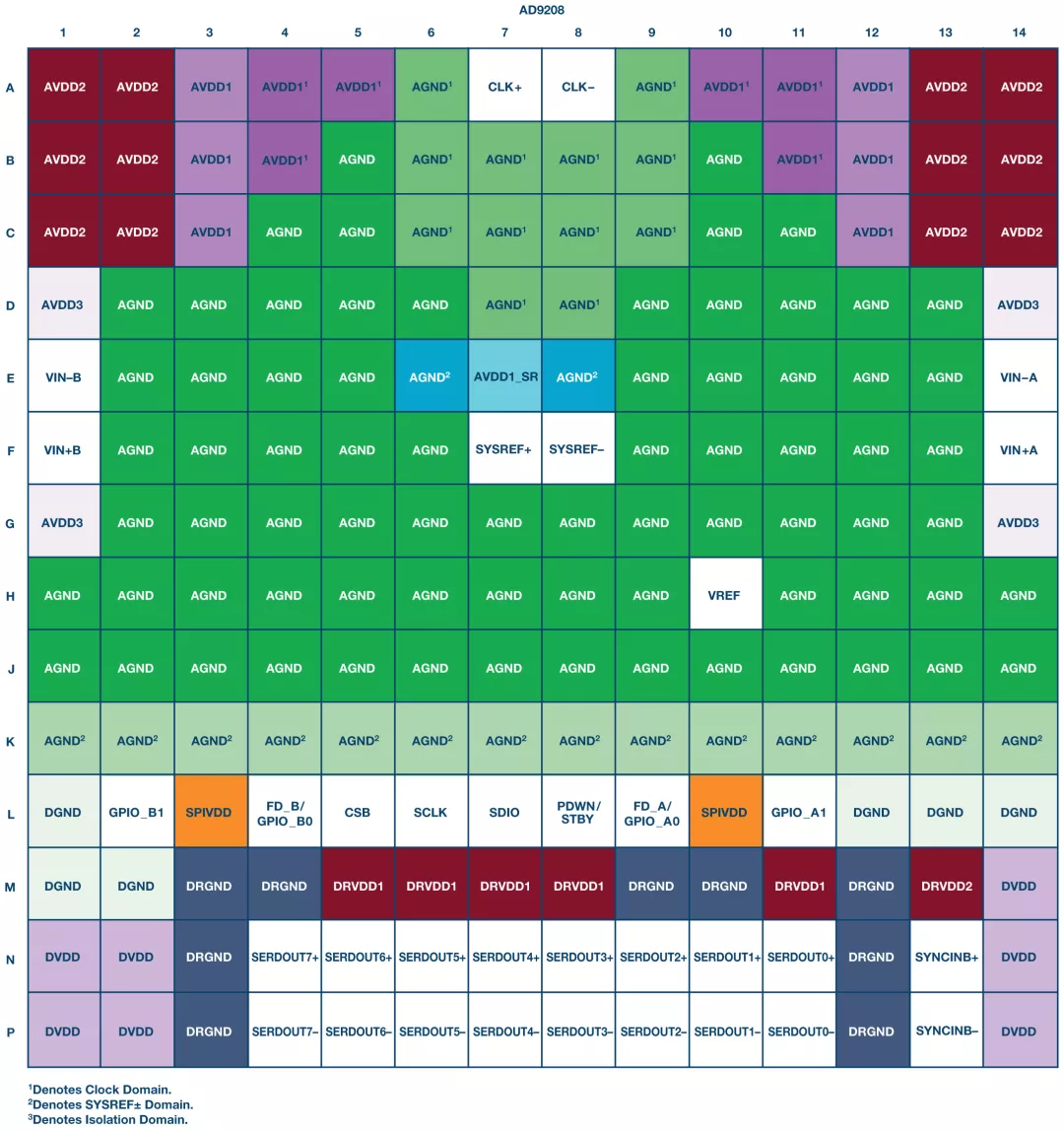

为了改善隔离,设计者必须考虑各种耦合机制,最明显的机制是通过共享电源域。如果电源域尽可能远离电路,那么共享同一电压轨(AD9208为0.975 V)的数字电路和模拟电路发生震颤的可能性将非常小。在硅片中,电源已被分开,接地也是如此。封装设计继续贯彻了这种隔离电源域处理。由此所得的同一封装内不同电源域和地的划分,如表2所示,其以AD9208为例。

表2:AD9208电源域和接地域

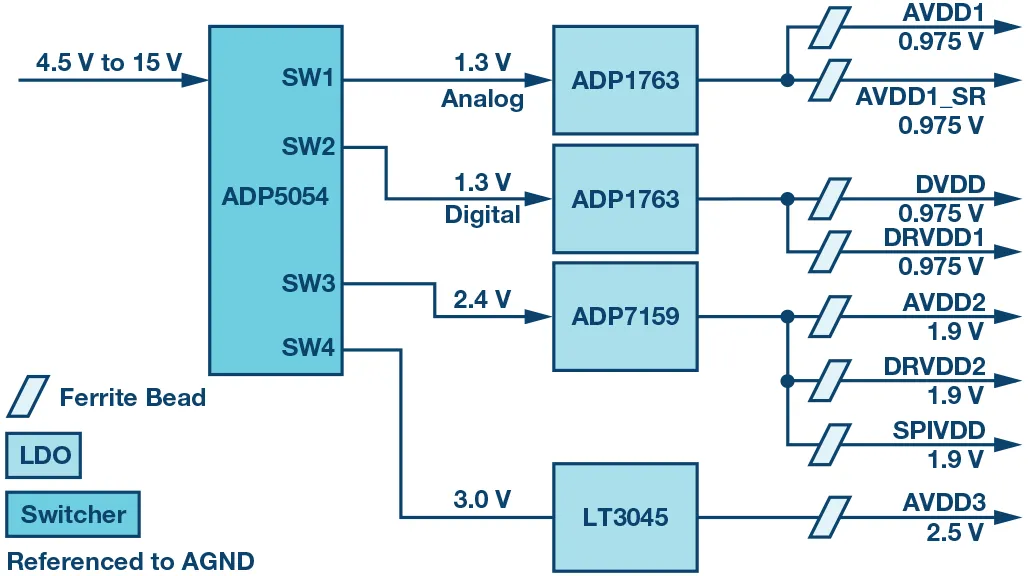

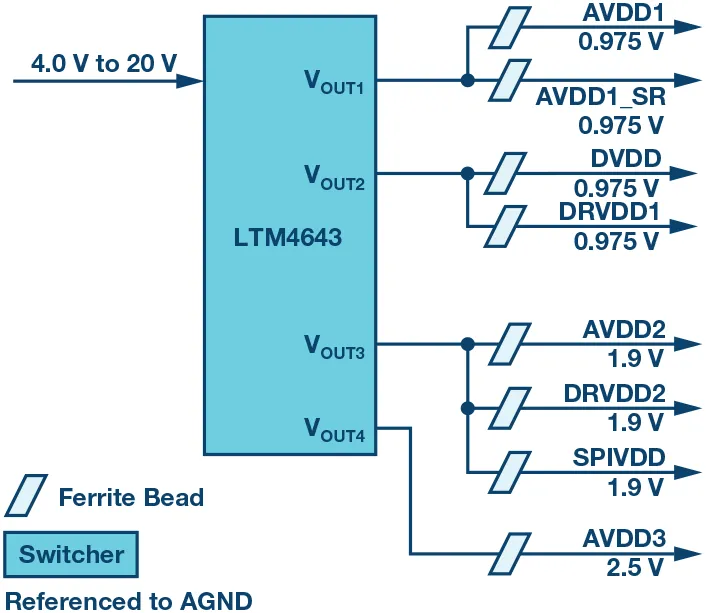

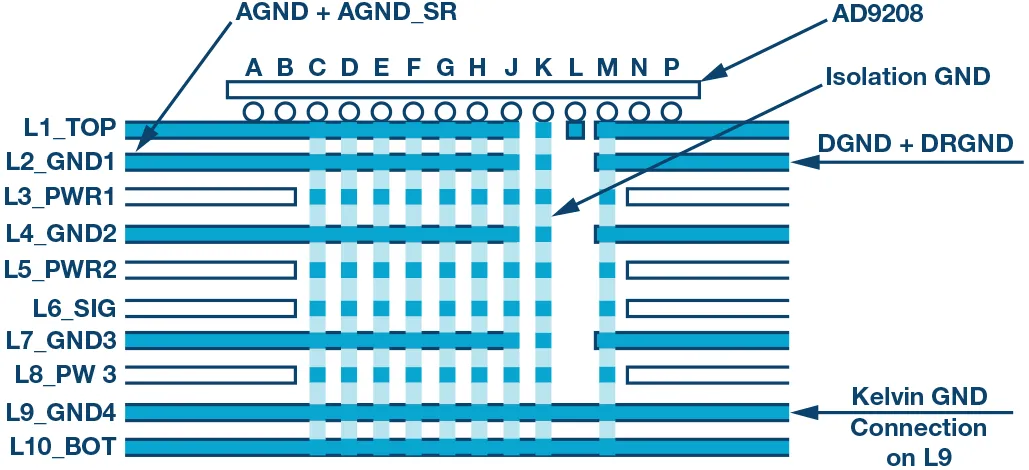

这可能会让系统设计人员惊慌失措。乍一看,数据手册给人的印象是这些域需要分开处理以优化系统性能。情况并不像看起来那么可怕,数据手册的目的仅仅是唤起人们对各种敏感域的关注,让系统设计人员可以关注PDN(电源输送网络)设计,对其进行适当的划分。共享相同供电轨的大多数电源域和接地域可以合并,因此PDN可以简化。这导致BOM(物料清单)和布局得以简化。根据设计约束,图2和图3显示了AD9208的两种PDN设计方法。

图3. AD9208 PDN,DC-DC转换器为所有域供电 图4. AD9208下方的AD9208-3000 EBZ PCB横截面

文章来源:亚德诺半导体

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

为机器视觉系统选择图像传感器,绕不开这三大关键考虑因素

电动汽车充电的热管理解决方案

重磅!嘉立创、一博科技、嘉捷通、金晟达等PCB行业巨头集结,一年只此一次!

功率器件模块:一种满足 EMI 规范的捷径

芯原戴伟民:AIGC为端侧AI带来巨大机会