利用基于 AI 的优化技术让高速信号问题迎刃而解

【导读】系统设计领域充满变数,确保信号完好无损地到达目的地还只是冰山一角。随着封装密度不断提高、PCB 线路不断细化以及频率不断飙升,这些错综复杂的问题也在不断演变,需要综合运用电气、机械、电磁和热动力学方面的专业知识。

系统设计领域充满变数,确保信号完好无损地到达目的地还只是冰山一角。随着封装密度不断提高、PCB 线路不断细化以及频率不断飙升,这些错综复杂的问题也在不断演变,需要综合运用电气、机械、电磁和热动力学方面的专业知识。

为了应对日益增长的复杂性和细微差别,系统需要达到最佳性能。而要实现这一目标,设计人员在发挥聪明才智的同时,还要借助机器的计算能力。遗憾的是,不同学科犹如一个个孤岛彼此分离,阻碍了专家之间的有效合作。要满足这些激增的需求,系统级优化已不再是一种“奢侈选项”,而是“必不可少”。

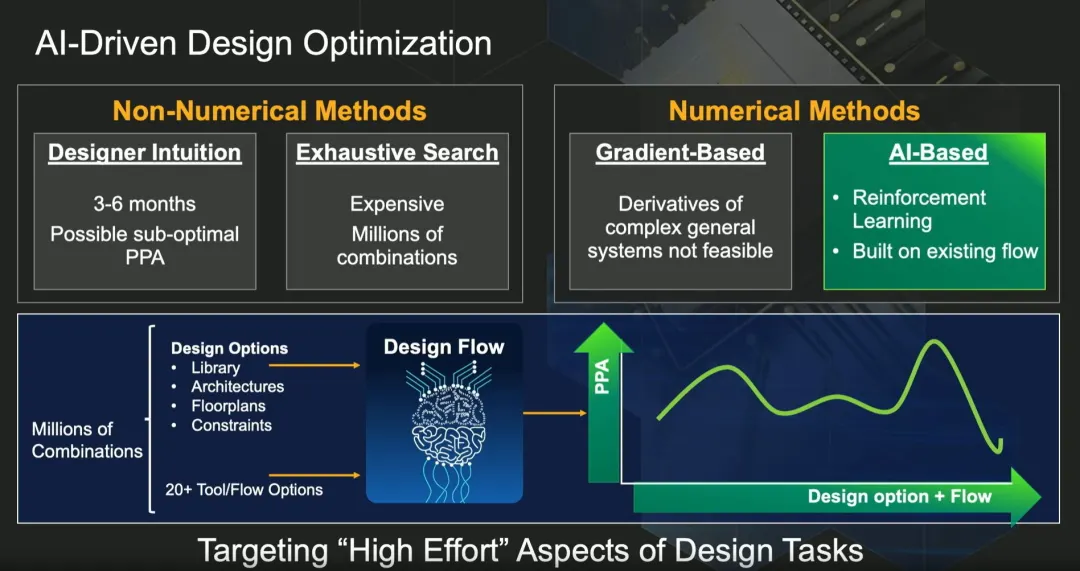

手动工作流程包括构建、测试、原型验证、改进和最终制造,这给设计优化造成了很大的阻碍。目前的设计优化方法在很大程度上依赖于设计人员的直觉,他们通过创建原型和运行仿真来评估设计是否符合目标。然而,如今的电子设计开始追求更强的性能、更高的复杂性和更紧凑的外形,单凭人类的直觉已经难以应对优化挑战。我们需要先进的优化方法来实现日益复杂的现代设计。

基于 AI 的优化

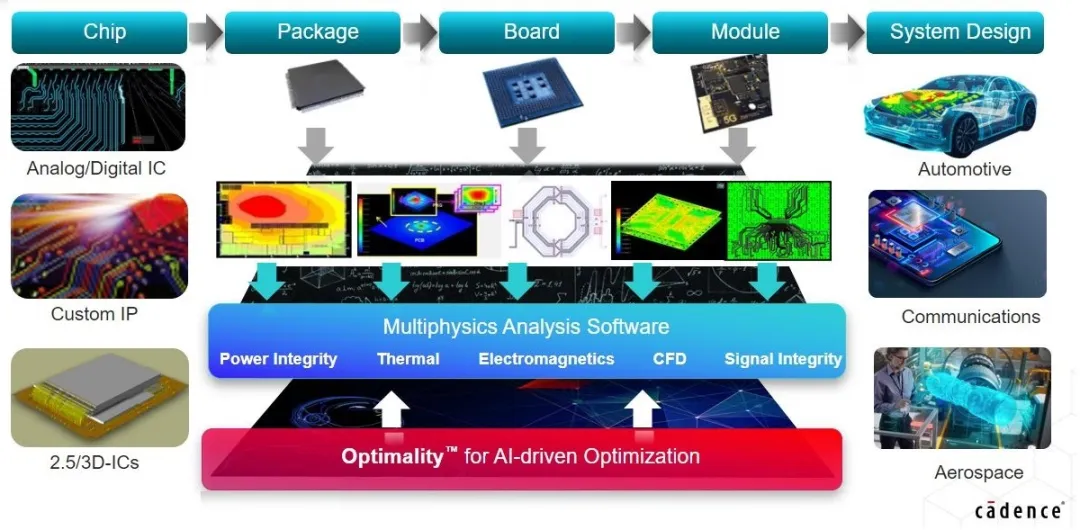

Cadence 推出了Optimality Intelligent System Explorer,这是一项全新的优化技术,利用 AI 帮助设计人员应对现代设计挑战。该技术具有多学科设计分析优化 (MDAO) 功能,可无缝执行从集成电路到封装,乃至电路板的系统级优化。将多物理场分析工具与 Optimality Explorer 集成,确保了预期结果万无一失。自动化大大加快了优化过程,工程师和设计师可以更轻松、更高效地实现目标。

Optimality Explorer 工作流程可指定输入参数,优化系统标准,并使用多物理场分析工具进行仿真。它能自动完成优化过程,生成优化设计和最终曲线。用户可以优化回波损耗、插入损耗、串扰隔离等参数以及眼图、抖动和比特误码率 (BER) 等系统标准。

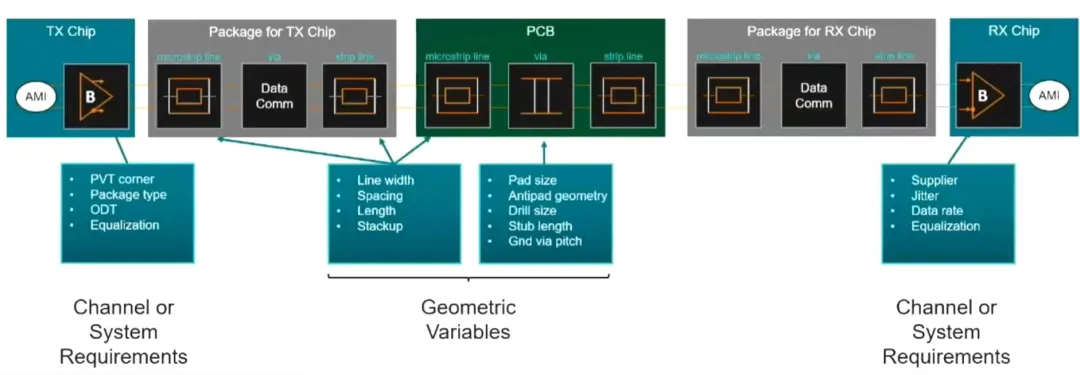

为实现有效优化,设计人员必须考虑线宽、间距、线长、走线堆叠、焊盘尺寸、隔离焊盘几何形状、钻孔尺寸和过孔 stub 长度等几何变量。在创建模型时,还必须考虑制程 (Process)、电压 (Voltage) 和温度 (Temperature) 组合,片内端接 (on-die termination, ODT),抖动均衡等参数。

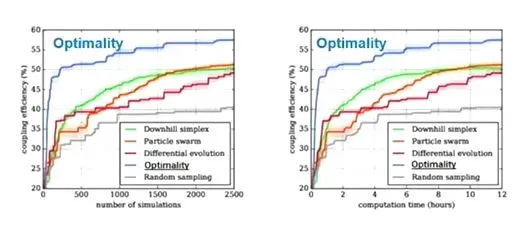

Optimality Explorer 旨在帮助设计人员进行无缝的设计优化,无需用户干预。其算法实现了优化过程的自动化,可提供流畅、便捷的用户体验。与传统方法相比,它能在不到 500 次的迭代中实现显著优化,加快设计收敛。Optimality Explorer 被称为 AI 驱动的设计同步多学科分析与优化工具。

Optimality Explorer 可高效、准确地仿真和优化复杂的 3D layout,处理传统上被认为具有挑战性的优化方案。该工具中包含用于 PC 封装互连的场求解器,可处理各种通常被视为具有挑战性的优化方案,如最大化交叉网格覆铜。

优化参数和注意事项

例如,在系统通信信道中,有发射器、接收器、PCB 互连、封装和中介层。这些器件经过抽象化,用作发射器-接收器的 IBIS-AMI 模型,发射器-接收器之间是走线和过孔。

为确保最佳信道性能,必须考虑各种几何变量,如线宽、间距、线长、走线堆叠、焊盘尺寸、隔离焊盘几何形状、钻孔尺寸和过孔 stub 长度。创建模型时还应考虑 制程 (Process)、电压 (Voltage) 和温度 (Temperature) 组,片内端接 (on-die termination, ODT) 和抖动均衡等参数。

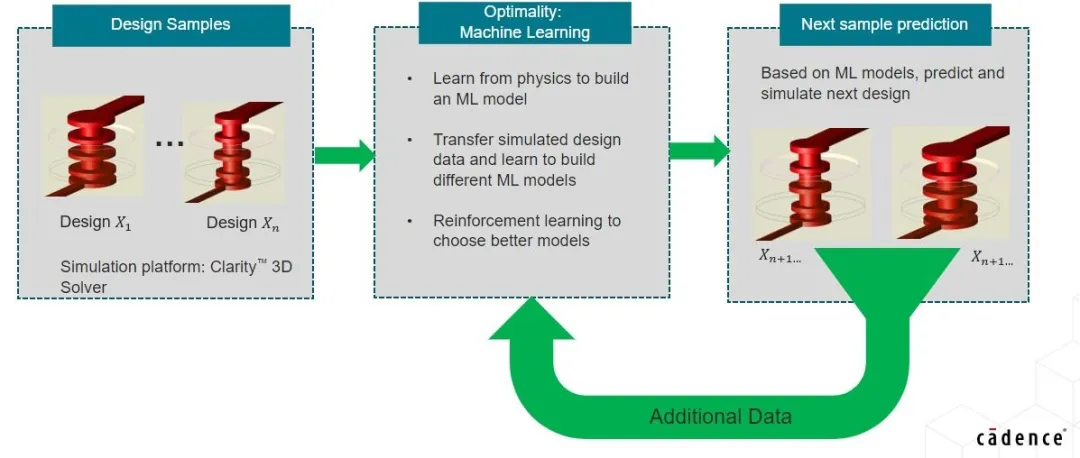

在优化过程中,必须指定需要优化的设计参数和想达到的优化目标。此外,还必须创建额外的代理模型 (surrogate model),以有效优化这些参数。

Optimality Explorer 基于随机搜索生成的初始数据集,构建并训练机器学习模型。它会不断分析仿真结果,更新设计变量,计算目标函数和约束条件,直到达到停止标准和收敛为止。

Optimality Explorer 旨在简化设计人员的优化过程,尤其是在需要考虑许多可调参数的情况下。其算法实现了优化过程的自动化,无需用户干预,并且易于使用。

传统方法需要 2500 次以上的迭代才能获得相当的结果,与之相比,Optimality Explorer 只需不到 500 次的迭代就能实现显著优化,可加快设计收敛。

利用 Optimality Explorer 提高效率

在复杂的电路 layout 中,仅使用单独的走线和过孔是不够的。需要将这些器件组合起来,创建互连设计,其中每个器件都会影响到其他器件的行为。

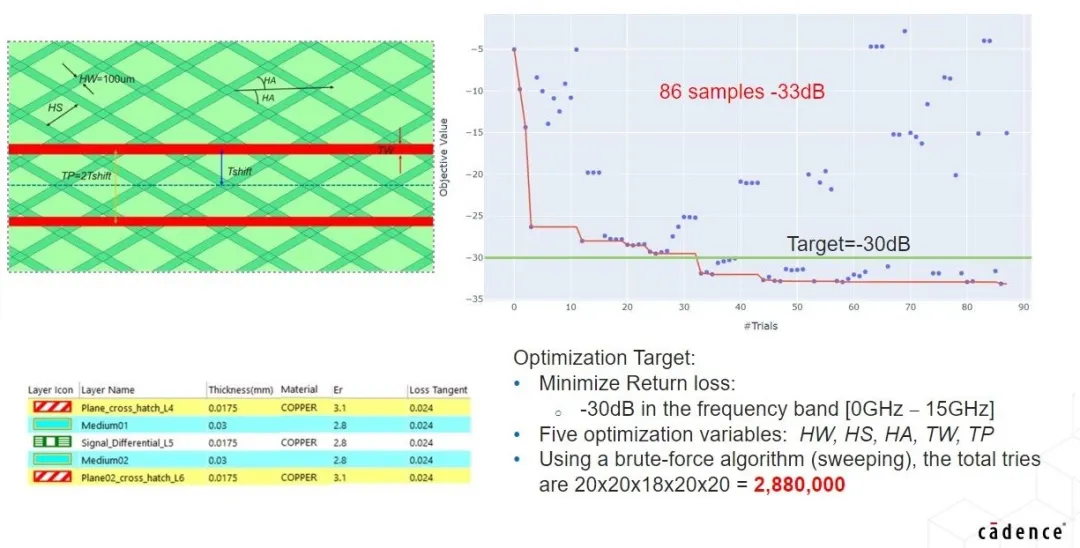

两个交叉网格覆铜平面之间的差分对

Optimality Explorer 可高效、准确地仿真和优化复杂的 3D layout,处理传统上难以优化的方案。该工具中包含用于 PC 封装互连的场求解器,可处理各种通常被视为具有挑战性的优化方案。例如,它可以最大限度地优化差分对设计中的交叉网格覆铜图案,从而获得更好的结果。Optimality Explorer 还能减少详尽扫描所需的仿真次数,更快地达到目标。

Optimality Explorer 可以优化布局前和布局后设计。例如,Optimality Explorer 对 RF 功率分配器进行优化,仅用 46 次仿真就达到了目标,而穷举法则需要 300 多万次仿真。Optimality Explorer 的多功能性还可扩展到处理具有许多参数的设计,例如,优化具有 16 个参数的微带贴片天线只需 71 次迭代。

展望未来:扩展 Optimality 平台

Optimality Explorer 工具背后的团队目前正在努力扩展该平台的适用范围,使之可以涵盖热学和流体动力学领域。这包括集成 Celsius 3D Solver 用于热分析,集成 CFD 工具用于流体动力学领域。此外,电气约束将被集成到 Allegro X Design Platform 现有的约束管理器中,为用户提供更全面的解决方案。开发团队将不断报告这些功能改进的最新进展。

推动电子系统的多物理场分析

解决现代系统中的高速信号优化问题是一项涉及多个维度的挑战。Optimality Explorer 突破了传统上极为消耗人力的优化流程的限制,以 AI 驱动技术取代了“设计-测试-改进”循环的传统交互流程,提供了一套更好的系统设计解决方案。Optimality Explorer 是电子设计领域的灯塔,指引设计人员自信穿梭于错综复杂的环境,在提供自动化技术的同时提高设计效率,为未来的综合设计解决方案铺平道路。

文章来源:Cadence楷登PCB及封装资源中

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。