如何防止数字MEMS传感器出现混叠现象

【导读】过去十多年来,基于微机电系统 (MEMS) 的设计人员一直选择使用数字式 MEMS 传感器,而不是模拟式。驱动这一趋势的原因是传感器产品的利用率、功能集、集成度和成本。选择数字式 MEMS 传感器时,工程师面临着诸如传感器量程、噪声、封装和电流消耗等设计决策。对于加速计等惯性 MEMS 传感器,设计人员还应考虑传感器的带宽特性,以避免不需要的信号混叠到传感器的信号链中。

过去十多年来,基于微机电系统 (MEMS) 的设计人员一直选择使用数字式 MEMS传感器,而不是模拟式。驱动这一趋势的原因是传感器产品的利用率、功能集、集成度和成本。选择数字式 MEMS 传感器时,工程师面临着诸如传感器量程、噪声、封装和电流消耗等设计决策。对于加速计等惯性 MEMS 传感器,设计人员还应考虑传感器的带宽特性,以避免不需要的信号混叠到传感器的信号链中。

本文将讨论传感器系统中的混叠基本原理,以及用于消除混叠误差的几种方法之间的取舍。

背景知识

MEMS 加速计1 已成为基于状态的监测 (CbM)、预测性维护 (PdM)、降噪、生物识别反馈和许多其他应用中进行振动检测的首选解决方案。与以前的压电和模拟传感器解决方案相比,数字加速计具有功耗低、成本低和封装小等主要优势。数字 MEMS 加速计的可扩展性使系统设计人员能够在系统中使用多个加速计,并在物理振动点远程部署传感器。这样,系统就能在本地检测惯性运动,以进行实时分析并立即采取行动,从而达到最佳运行状态。

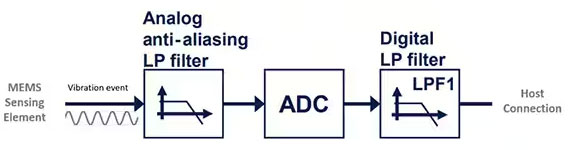

图 1:数字加速计的典型应用。(图片来源:STMicroelectronics)

由于数字加速计的全集成特性,设计人员必须考虑传感器的带宽和频率响应。这一点在振动应用中尤为明显,因为设计人员必须防止输入频率在传感器输出中出现混叠。

奈奎斯特定理

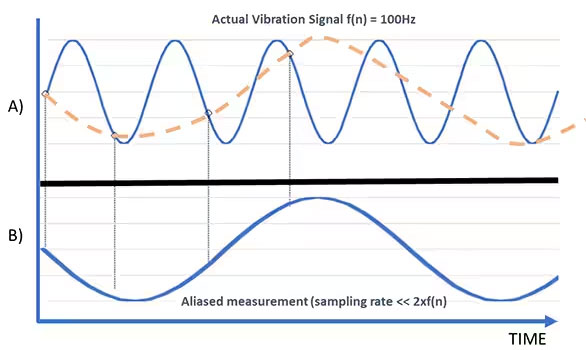

当传感器采样速度过慢,无法准确测量输入信号时,加速计系统中就会出现混叠现象。在振动检测等 MEMS 传感器应用中,混叠会导致灾难性故障,因为实际振动信号中是可能不存在混叠信号的。

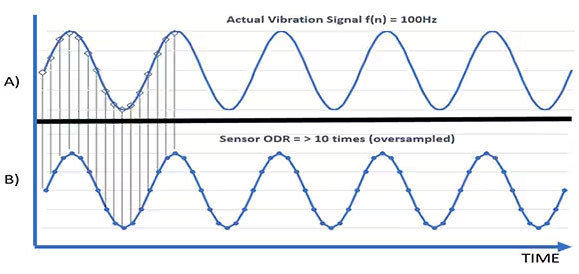

图 2 所示为一种混叠情况。振动频率比采样频率高 2 倍,导致结果出现混叠波形。实际震动中不存在混叠信号,而是由于对输入振动的采样不足而产生的假象。混叠信号来自ADC在振动的上坡和下坡时采集的样本,经过插值后呈现出一种与实际振动不同的波形。

图 2:低采样率导致的混叠结果。(图片来源:STMicroelectronics)

等式 1 着重强调了数字信号处理中采样率的既定规则,即奈奎斯特定理。根据该规则,采样频率 f(采样)至少是系统中最高频率 (F) 的两倍才能防止混叠出现。![]() 等式 (1)

等式 (1)

例如,对于 100 Hz 的振动,只要采样频率至少高于 200 Hz 时才能检测没有出现混叠的振动信号。如图 3 所示,当采样率比最小频率快得多时,就能正确捕捉到实际振动信号。超采样是一种数字滤波方法,但需要注意的是,仍可能会有一些不需要的信号泄漏到信号链中。

图 3:超采样用于防止传感器输出中出现混叠。(图片来源:STMicroelectronics)

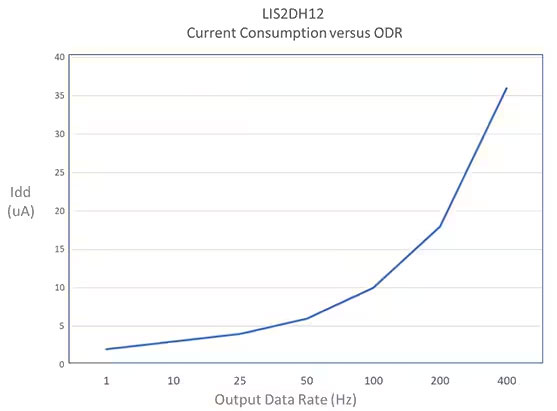

使用超采样作为减少混叠的方法的缺点是,高采样率导致显著更高的功耗。典型传感器的采样率或输出数据速率 (ODR) 会直接影响功耗,如图 4 所示。采样率越高,电流消耗越大。

图 4:加速计的电流消耗。(图片来源:STMicroelectronics)

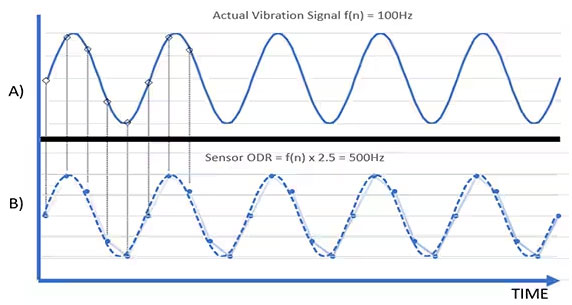

如图 5 所示,降低采样率,使其更接近奈奎斯特频率,就可降低功耗。这里的采样率降至 500 Hz,约为目标频率的 2.5 倍。在 500 Hz 频率下,实际振动波形仍可通过插值法再现,与 10 倍目标频率下的采样相比,电流消耗将有所减少。

图 5:将采样率降至振动频率的 2.5 倍。(图片来源:STMicroelectronics)

这与上一个例子相比有所改进,但仍有可能将输入信号中的某些意外高频成分混入传感器信号链中。

采样率说明

在使用加速计时,最常见的问题之一是如何为具体应用选择合适的采样率。选择采样率时,往往需要在性能和电池寿命之间进行权衡。高采样率会产生庞大的数据文件,不仅难以处理,而且会阻碍通信,降低能效。另一方面,采样率过低会使系统失真,如前面的示例所示。

幸运的是,我们在选择最低采样率方面已经有了成熟的指导原则。在功耗不受限制的应用中,采样率可设置为数倍于事件频率。但是,即使采样率较高,由于振动数据和噪声的模拟性质,采用数字滤波时也有可能出现混叠。

抗混叠滤波器(AAF)

除了功耗增加外,数字超采样还有其他缺点。振动并不总是完美的正弦波,往往具有谐波和噪音等高频成分。为减少这些影响因素,可在信号采样前使用低通滤波器消除任何无关的高频信号。这种低通滤波器也称为抗混叠滤波器,嵌入在某些型号的 MEMS 加速计中。

图 6:模拟抗混叠(低通)滤波器。(图片来源:STMicroelectronics)

抗混叠滤波器的工作原理与低通滤波器基本相同。在 ADC 采样之前,AAF 会消除高频成分。AAF 必须置于 ADC 之前,才能执行概念要求。如果将 AAF 放在 ADC 之后,它就变成了数字滤波器,数字滤波器和超采样的缺点已在前面讨论过。

带嵌入式AAF 的加速计系列

LIS2DU12 是在模拟前端内置抗混叠滤波器的 3 轴数字加速计系列。LIS2DU 有三个版本,除基本设计外,每个版本都有一套独特的功能。这三款器件均采用 STMicroelectronics 的 2 mm x 2 mm 12 引线 MEMS 加速计封装。每款器件都采用相同的超低功耗架构,抗混叠滤波器使其具有市场上最低的电流消耗。下面重点介绍该器件系列的比较。

LIS2DU12:具有抗混叠和运动检测功能的超低功耗加速计

LIS2DUX12:嵌入了抗混叠和机器学习核心 (MLC) 的超低功耗加速计

LIS2DUXS12:带 Qvar、MLC 和抗混叠功能的超低功耗加速计

在 LIS2DU 系列中,低通滤波器在 ADC 之前的信号链中实体化,以便在数字转换之前消除噪声。

除了抗混叠滤波器这一重要新增功能外,LIS2DU12 还具有多项先进的数字功能。这些特性旨在通过实现一些常用功能(如自由落体、倾斜、轻触检测、定向和唤醒)来减轻主微控制器的负担。LIS2DUX12 还包含一个嵌入式机器学习内核 (MLC),可针对具体应用设计开发更先进的功能。

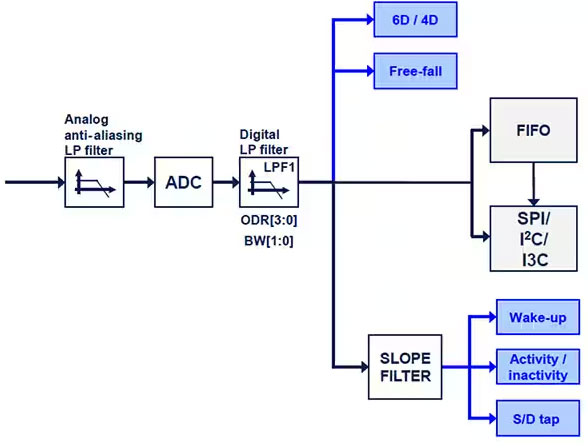

图 7:LIS2DUX12 加速计滤波链。(图片来源:STMicroelectronics)

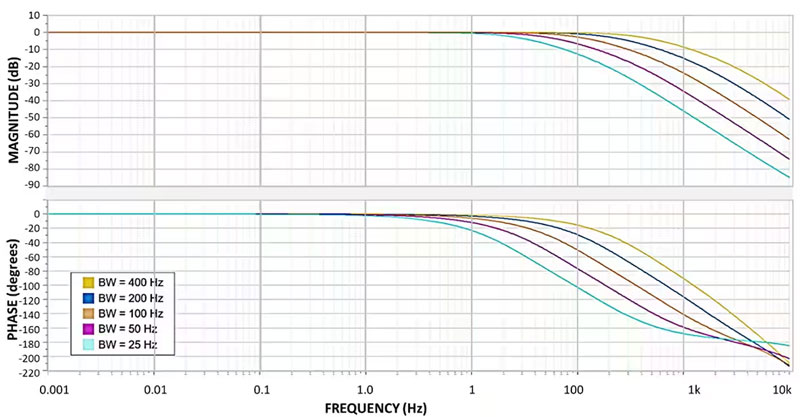

LIS2DU12 模拟抗混叠滤波器的频率响应如图 8 所示。下面每条曲线的 25 Hz 至 400 Hz 频率值指的是滤波链带宽值。

图 8:LIS2DU12 模拟抗混叠(低通)滤波器。(图片来源:STMicroelectronics)

最终结果是,LIS2DU12 系列加速计的工作电流大大降低,而精度却与上一代加速计相同。除了在所有三个版本中嵌入抗混叠滤波器外,LIS2DUX12 和 LIS2DUXS12 是 STMicroelectronics 的首款包含嵌入式 MLC 的消费类 MEMS 器件。

结束语

混叠是导致系统故障的一个重要误差源。为了减轻混叠影响,设计人员必须首先了解系统,并预测检测链中所有组件的频率成分。奈奎斯特定理定义了要测量的最高频率的最小采样率。

超采样可以减少混叠影响,但功耗较高。在许多应用中,防止混叠的最佳方法是在 ADC 将采样转换到数字域之前,使用抗混叠滤波器消除不需要的频率。

通过考虑一些指导原则,设计人员可以为具体应用选择合适的采样和滤波技术。

(作者:Tom Bocchino, STMicroelectronics)

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

用于电动汽车快速充电的双向拓扑:优化尺寸、功率、成本或简单性的选择

DIY一个高保真音频放大器电路

运动传感器风扇电路图分享

MOS管在户用储能上的应用

电流传感器磁场干扰管理