LMK04832-SP是符合 JESD204B 标准的空间级超低噪声时钟抖动清除器

产品详情

描述:

LMK04832-SP 是一款高性能时钟AD829AQ调节器,支持 JEDEC JESD204B,适用于空间应用。

来自 PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动七个 JESD204B 转换器或其他逻辑器件。可以使用 DC 和 AC 耦合来提供 SYSREF。不限于 JESD204B 应用,14 个输出中的每一个都可以单独配置为传统时钟系统的高性能输出。

LMK04832-SP 可配置为在双 PLL、单 PLL 或时钟分配模式下运行,带或不带 SYSREF 生成或时钟恢复。PLL2 可以与内部或外部 VCO 一起工作。

高性能与功率和性能之间的平衡能力、双 VCO、动态数字延迟和保持等特性相结合,使 LMK04832-SP 能够提供灵活的高性能时钟树。

LMK04832-SP 采用 10.9mm × 10.9mm、64 引脚 CFP 封装。

特性:

●贴片#5962R1723701VXC

○总电离剂量 100 krad(无 ELDRS)

○SEL 免疫 >120 MeV × cm 2 /mg

○SEFI 免疫 >120 MeV × cm 2 /mg

●多模式:双 PLL、单 PLL 和时钟分配

●6GHz 外部 VCO 或分配输入

●PLL2

○–230 dBc/Hz 的 PLL FOM

○–128 dBc/Hz 的 PLL 1/f

○鉴相器速率高达 320 MHz

●多达 14 个差分设备时钟

○CML、LVPECL、LCPECL、HSDS、LVDS 和 2xLVCMOS 可编程输出

●多达 1 个缓冲 VCXO/XO 输出

○LVPECL、LVDS、2xLVCMOS 可编程

●SYSREF 时钟的 25 ps 步进模拟延迟

●设备时钟和 SYSREF 的数字延迟和动态数字延迟

●环境温度范围:–55 °C 至 125 °C

应用:

●通信负载

●雷达成像有效载荷

●命令和数据处理

参数:

功能:单环锁相环

输出数量:15

RMS 抖动 (fs):54

输出频率(最大)(MHz):3255

输入类型:LVCMOS、LVDS、LVPECL

输出类型:CML、HSDS、LVCMOS、LVDS、LVPECL

电源电压 (Min) (V):3.135

电源电压(最大)(V):3.465

特征:JESD204B

工作温度范围(℃):-55 到 125、25 到 25

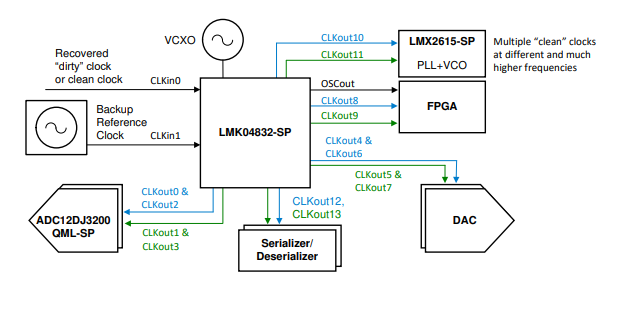

◆LMK04832-SP 简化原理图