聊聊CPU中最基础的逻辑门

这是《CPU Logisim设计》的第二个章节。我最近一直在设计流水线为基础的RISC-V架构CPU,所以一直没有时间更新,我们这次抽空来聊聊CPU中最基础的逻辑门。

CPU大部分是由逻辑门构成的(话不能说太绝对),而逻辑门无外乎就是与门、或门、非门这三种。但在开始之前我们先要了解一下CPU中的数制。CPU不同于人脑,CPU采用的是二进制,也就是0和1,比如3这个十进制数等于二进制数11。那么为什么要采用二进制呢?道理很简单却也很复杂。简单来讲电路设计成二进制是更为方便的,因为0和1可以用电压有无来代替,其抗干扰性强;复杂来讲CPU使用二进制还涉及到布尔逻辑、历史遗留等一系列问题。传闻前苏联曾经研制出三进制的计算机,但最后因为性能不优良而被放弃了。所以其实非二进制也不是不可以。

讲完了数制,我们开始聊逻辑门。首先要注意一点,逻辑门是一种客观存在的电路结构,其物理微观实质比较复杂,我挖个坑……我们这里暂时只讨论宏观现象。

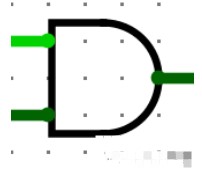

首先是与门(AND)。

左边这两条小短线(不一定就只有两条,可以大于等于两条)是输入,右边就是输出了。中间那个“半圆形”的就是标准的与门了。

与门的特点是:输入都是1时,输出才是1。图中亮绿色的是1,暗绿色是0,所以输出是0,没有问题。

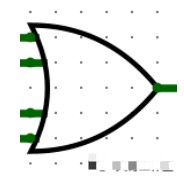

再就是或门(OR)。

或门的特点是:输入但凡有个1,输出就是1。我特意找了个四个输入的或门,这四个输入都为0,所以很不幸输出是0。

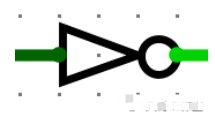

然后是非门(NOT)。

非门就更简单了。其特点是:输出是输入的取反。就是说输入是1,输出是0;输入是0,输出就是1。另外,不同于以上两种逻辑门,非门只有一个输入。

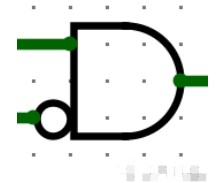

最后,给你们看一个奇怪的东西。

像不像与门长了个瘤?这个其实是与门和非门的结合体,同理还有或门和非门的结合体。其中非门被简化成了一个圆,用于取反与门的下面一路的输入。因为非门的逻辑实在是太简单了却又太容易被用到,这种画法可以有效的节省画板空间。

此外还有异或门(XOR)、同或门(XNOR)等门电路,它们无不是从与、或、非三种逻辑门上组合而来。这种组合而来的电路又被称为组合逻辑电路。与之相对的概念是时序逻辑电路。

那么这些逻辑门能做什么呢?

且听下回分解。

审核编辑:刘清