外资法人预计台积电 2nm 采用 GAAFET 路线,此前宣布 2025 年量产

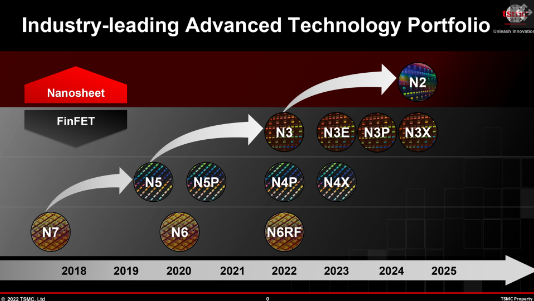

IT之家 9 月 4 日消息,3nm 时代,三星选择采用环绕栅极?(GAAFET)?晶体管架构打造 3nm 芯片,而台积电则延续了鳍式场效应管(FinFET)的方案,预计台积电?3nm(N3)芯片将于今年下半年投产。

台湾《经济日报》称,虽然在 3nm 世代略有保守,但无论如何,鳍片 (Fin) 宽度都已经接近实际极限,再向下就会遇到瓶颈,所以外资法人预估台积电 2nm 先进制程将采用环绕式闸极场效电晶体 GAAFET 高端架构生产 2nm 芯片。

根据台积电官网显示,台积电将持续与全球 16 家 EDA 厂商组成电子设计自动化联盟,其中就包括全球前 5 大 EDA 厂商。

美系外资法人指出,台积电在先进制程的 EDA 软件工具方面与美国厂商关系非常密切,其多数高端设备与 IP 不仅由美商供应,另外科磊(KLA)制程监控设备以及 ASML 的极紫外光 EUV 光刻机,也很难由日本、欧洲、甚至中国厂商取代。

外资法人表示,未来 5 年至 10 年,全球先进晶圆制程仍将以美系 EDA 软件(目前主要是新思科技、益华电脑以及西门子)和矽智财 IP 为核心,设计或制造芯片。

尽管 EDA 工具高度集中在美国企业名下,不过其他大厂在?EDA 方面并未缺席,例如联发科 5 月上旬与台大电资学院及至达科技合作,将 AI 人工智慧技术应用于 IC 设计,带动 EDA 智能化发展。

鸿海集团也同样正在积极布局半导体芯片设计,旗下工业富联在 7 月中旬透露他们正布局半导体锁定先进封装、测试、装备及材料、电子设计自动化软件、芯片设计等领域。

亚系外资法人指出,2020 年全球 EDA 市场规模约 115 亿美元,预估今年规模逼近 134 亿美元,尽管规模不大,却直接关系着全球超过 6000 亿美元规模的半导体产业、以及全球数十兆美元规模的数字经济发展。

对于芯片需求前景,台积电称其 2023 年的增长将由先进技术支撑,高性能计算(HPC)将成为长期增长的主要引擎。公司目前预计 2023 年产能利用率将保持良好。

在下一代芯片投产时间点方面,台积电强调?3nm(N3)芯片将于今年下半年投产,明年上半年贡献营收。IT之家提醒,台积电的 3nm 工艺有众多衍生版本,包括 N3、N3P、N3S、N3X、N3E,将会陆续在未来两三年内量产。

对于 2nm 芯片(N2),台积电重申其将于 2025 年实现量产。2nm 芯片是台积电的一个重大节点,该工艺将会采用纳米片晶体管(Nanosheet),取代鳍式场效应晶体管(FinFET),这意味着台积电工艺正式进入 GAA 晶体管时代。其中,2nm 芯片相较于 3nm 芯片,在相同功耗下,速度快 10~15%。在相同速度下,功耗降低 25~30%。

财报显示,台积电第二季度 5nm 制程晶圆出货量占据公司营收的 21%(前季 20%),7nm 制程晶圆出货量占据公司营收的 30%(前季 30%),本季度 5nm 制程工艺营收继续提升,但还未超过 7nm 制程工艺带来的营收。此外,台积电先进制程 (7nm 及更先进制程) 营收总占比达到 51%,较前季的 50% 继续扩大。