三星静候台积电「犯错」

四个月前,三星电子副董事长李在镕开启了自己的访欧之旅,最关键的还是荷兰,不仅与多名 ASML 高层举行了会谈,转头还向荷兰总理要起支持:

千万确保 ASML 稳定供应 EUV?光刻机。

过去两年蔓延全球的芯片短缺问题,主要还是局限在成熟制程,但问题已经要蔓延到了先进制程。据 6 月初 WSJ 报道 ,部分台积电客户收到警告,表示该公司未来两年扩产速度将不如预期,主因是包括 EUV 光刻机在内的制造设备缺少,分析师指 2024 年先进制程工艺的缺口可能高达 20%。

ASML EUV 光刻机零部件,图/ASML

但 ASML 产能终究还是有限,甚至三星自身的战略也有了变化。

据 10 月 25 日韩国经济新闻的报道 ,三星电子调整了战略方向,将扩大投资成熟制程工艺。三星电子半导体代工事业部计划到 2024 年将传统和特色工艺的数量增加 10 个以上,到 2027 年将对应产能提高到 2018 年的 2.3 倍。

传统工艺是 10nm~180nm 等半导体代工企业从过去开始进行技术开发的过程中诞生的「标准」工艺;特色工艺是针对特定客户需求将传统工艺进行定制化改进。

上周还有消息传出 ,三星考虑将旗下更多芯片委外代工,除了已有的圆晶代工伙伴联电,还会新增世界先进和力积电两家协助芯片代工,主要仍是成熟制程。

在此之前,三星一直致力于在最先进的制程上与台积电竞争。今年 6 月,三星 3nm 制程工艺正式量产,并首次用上全环绕栅极晶体管技术(以下简称 GAA)。台积电则在近日再次对外确认,3nm 将在今年第四季度晚些时候开始量产,预计 2023 年开始满载运行。此外,台积电还指出在 2nm 工艺上才会引入 GAA 技术。

一方面在 3nm 上「领先」台积电一步,另一方面却在加大自身和委外成熟制程的产能。常识告诉我们,资源有限才所以需要资源配置,三星在扩大成熟制程工艺投资的同时,就要相对应缩减在先进制程上的投入比例。

这很矛盾,但首先三星在先进制程上的「领先」本身就存在问题。

「虚假」的 3nm,跌倒的三星

过去几年,芯片代工厂在制程的「文字游戏」上愈演愈烈,英特尔、三星、台积电对外说的同一纳米制程实际上相差甚大,如英特尔的 10nm 制程工艺实际相近台积电和三星的 7nm。

三星 3nm 和台积电 3nm 同样存在很大的不同。从性能的角度看,三星 3nm(3GAE)工艺的晶体管密度为 1.7 亿/平方毫米,大大低于台积电 3nm(N3)工艺的 2.9 亿/平方毫米,反倒更接近台积电 5nm 和英特尔 7nm 的水平。

另一方面,三星在 3nm 节点首次引入 GGA 技术,有分析指该技术尚不成熟。目前尚不明晰三星引入 GGA 技术带来的影响程度,但据中国电子报近期的报道,三星在先进制程芯片上深陷良率的泥沼,3nm 良率仅为 35%,台积电 3nm 良率则达到了80%。

再加上此前三星在 4nm 上工艺表现,更多的高端客户都在流向台积电,包括长期选择三星半导体进行芯片代工的高通。

去年底,高通发布全新命名的骁龙 8 Gen 1,但这块 SoC 由于在发热和功耗上存在重大问题,很大程度上影响了?Android?旗舰在高端手机市场的表现。后续终于转而采用台积电 4nm 工艺代工骁龙 8 Gen 1+,才终于在市场上挽回一点口碑和认可。

到了下一代骁龙 8 Gen 2,高通更是直接选择了台积电 4nm。再加上苹果、英伟达、AMD、联发科等,台积电几乎攘括了全世界最顶尖的芯片厂商。而三星的首发客户,却是一家中国矿机芯片厂商 PanSemi。

对三星来说,这无疑是相当糟糕的事情,毕竟目前新建一条 3nm 产线的成本约为 150-200 亿美元,巨大的资金投入需要更多更高端的客户订单。

但三星眼下除了在台积电的产能外获得订单,以及在价格上做出竞争以争取对价格更敏感的客户,似乎只能在更先进的 2nm 做出突破,或是在传统工艺市场抢占台积电的份额。

事实上,除了在先进制程上领先,台积电 46% 的收入都来自传统和特色工艺,尤其是目前市场占主流需求的 28nm,考虑到这些制程工艺都是台积电过去 35 年推进工艺过程中「留下」的,占主要成本的圆晶厂投入基本都已收回,利润更是可观。

三星作为后进者,过去的选择是在与台积电竞争先进工艺的同时,积累不同阶段工艺,如在图像传感器(CMOS)方面,传统使用 28nm 工艺,三星却将用于高级图像传感器的 17nm 工艺,与索尼竞争 CMOS 市场。

而引导三星的,大概是「在 2030 年成为世界第一的半导体代工企业」的目标。当然,这也意味着需要超越台积电。

失效的摩尔定律,领先者的困境

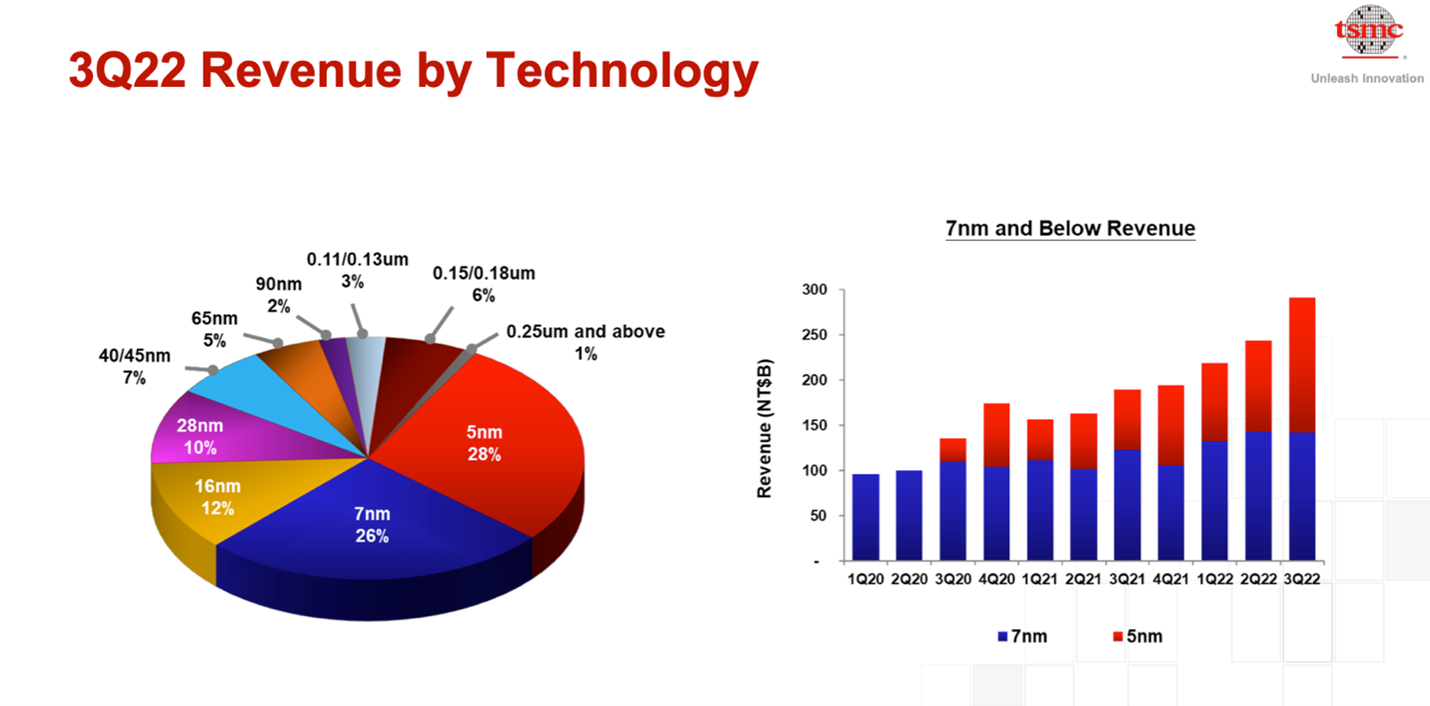

毫无疑问,台积电不仅是全球最大的半导体代工企业,也在 7nm 和 5nm 的关键节点上成为了最大的赢家。根据台积电今年第三季度财报,7nm 和 5nm 贡献的收入已经占到了整体的 54%。

这种优势目前来看还会继续延续到 3nm 节点。苹果 A17 芯片基本确认将由台积电独家生产,也有多个消息源指出 M2 系列高性能处理器也将由台积电独吞,此外还有高通将在 2023 年发布的旗舰芯片,甚至是英特尔的 15 代酷睿。

超能网引述 Twitter 用户 @OneRaichu 指出,Arrow Lake-P 移动处理器将采用英特尔自己的 20A(原英特尔 5nm)工艺,Arrow Lake-S 桌面处理器采用台积电的 N3(3nm)工艺。

至于 2nm 的节点,台积电和三星都计划在 2025 年实现量产,英特尔则更加激进地将 18A(接近台积电 2nm)工艺定在 2024 年量产。但随着制程逼近物理极限,摩尔定律越来越不能指导整个半导体行业继续前进了。

1965 年,时任仙童半导体公司研发总监的戈登?摩尔发文预言:

在最小成本的前提下,单个芯片上的元器件数量基本上是每一年翻一倍。并且至少在未来十年保持这个增长速度,到 1975 年单个芯片上将集成 65,000 个元器件。

这段被称为「摩尔定律」的话后来逐渐演变成:

1.?集成电路上集成的晶体管数目,每 18 个月翻一番;

2.?CPU?性能每 18 个月提高一倍,或价格下降一半;

3. 同样钱买到的计算机性能,每 18 个月翻一番。

根据台积电的数据,摩尔定律指导整个半导体行业的时间远远超越戈登·摩尔划定的寿命,如今一个 IC 设备可以容纳多达 1000 亿个晶体管——这已经是极限了,即便是在苹果 A16 小小的芯片上也能放下 160 亿个晶体管。

但正如英伟达 CEO 黄仁勋最近的提醒——「摩尔定律已经死了,」逼近物理极限的制程工艺则是最后也最关键一堵墙。当硅基芯片突破 1nm 之后,量子隧穿效应将使得「电子失控」,芯片失效。事实上,量子隧穿效应 5nm 甚至 7nm 以下就已经存在。

与此同时,量产先进制程芯片的成本越来越高。3nm 芯片的设计动辄就要 15 亿美元,到了 2nm,台积电仅产能布局就计划投入 1 万亿新台币(约 2290 亿人民币),超过华为?2021 年整体收入三分之一。

「台积电可能会失败。随着移动到下一个技术节点变得更加困难,任何人都可能跌倒,」英国《金融时报》引述经济历史学家克里斯·米勒的看法称,「或者,如果未来几个技术节点的过渡比我们预期的更为艰难,台积电的优势可能会变得不那么有意义。」

对后进者来说,这是赶超台积电——也是全球顶级水平最好的机会,至于整个行业的问题,毕竟天塌了还有个高的顶着,这大概也是强者的烦恼吧。

更多信息可以来这里获取==>>电子技术应用-AET<<