从单一组件到完备子系统,PCIe?6.0应用门槛大幅降低

继今年3月推出PCIe?6.0控制器之后,Rambus日前再接再厉,推出由PHY和控制器IP组成的PCIe?6.0接口子系统。Rambus战略营销副总裁Matt?Jones表示,该子系统已经通过了硅验证,技术成熟度可靠,可大幅降低用户开发PCIe?6.0技术的难度。相比PHY和控制器单独授权,两者结合的子系统方式,可以让SoC开发人员无需再重复做大量冗杂的验证工作,从而将更多时间专注在产品差异化和算法开发上。

作为在CPU、GPU、FPGA和特定工作负载加速器等各种计算节点之间快速传输数据的重要骨干,自21世纪初正式创立以来,PCI?Express(PCIe)接口就成为了数据中心和计算应用中芯片间数据传输的行业标准。随着PCIe标准的快速发展,2022年1月,PCIe?6.0相关规范正式出台,标志着我们从此进入了PCIe?6.0时代。

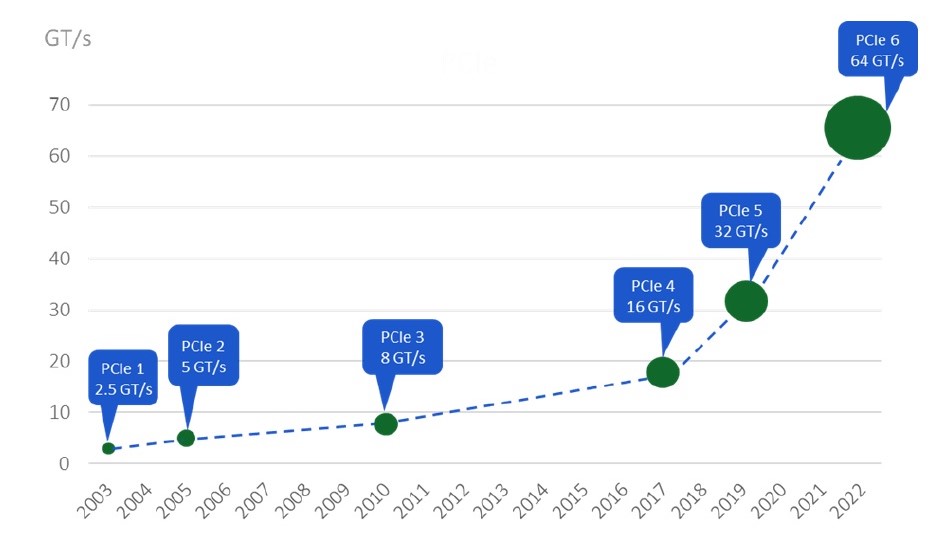

下图清晰的展示了PCIe标准的演进趋势。可以看出,从PCIe?2.0到3.0/4.0,分别花费了5年和7年的时间,但从PCIe?4.0到5.0,再到6.0,时间间隔却分别只有2年和3年,而且PCIe?6.0?64GT/s的传输速度也是3.0标准的8倍。

图1:PCIe性能加速曲线(图源:Rambus)

PCIe标准加速演进背后的直接推手,当然主要源于全球数据总量的爆炸式增长——从现有应用到以人工智能、机器学习(AI/ML)为代表的新兴应用,都在不断生成更多的数据。IDC数据显示,2021年上半年,中国大数据平台的整体市场规模达到了54.2亿元,同比增长43.5%。

PCIe?6.0的新特性

作为全新一代规范,PCIe?6.0对比之前的PCIe技术有非常多的技术改进,但最主要的三处改变是值得高性能计算、AI和存储SoC开发者们关注的:

- 数据速率从32GT/s翻倍至64GT/s

- 从NRZ编码转换到PAM-4编码,以及由此带来的纠错影响

- 从传输的可变大小数据包(TLP)到固定大小数据包(FLIT)

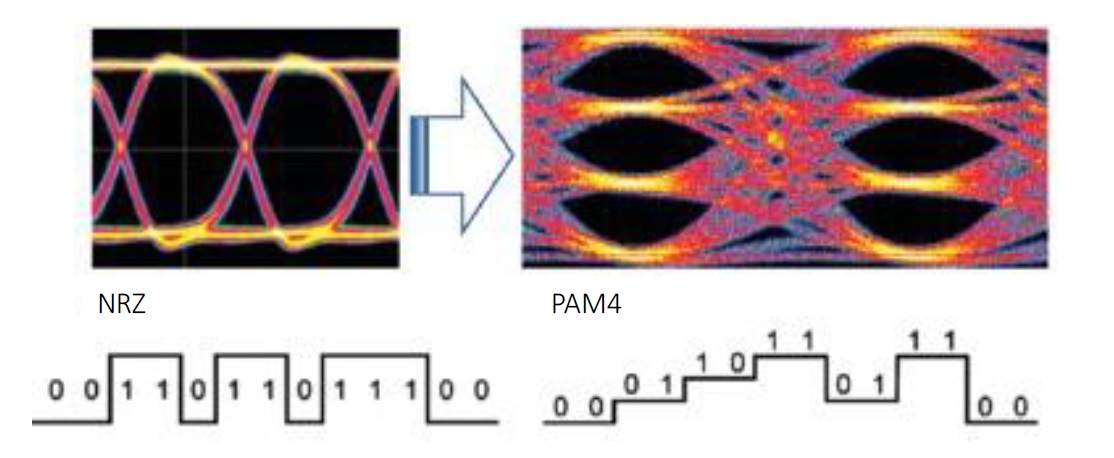

PAM4调制信号,也就是四电平脉冲幅度调制的采用,对PCIe?6.0的实现非常关键。因为在PCIe?6.0之前,各代PCIe采用的都是NRZ调制信号,即不归零编码,它采用0或1两个电压等级,每一个时钟周期只能传输1bit的信号,但PAM4每个时钟周期的数据传输可以达到2bit。

这就意味着,在同样的电压波动范围之内和同样的时钟周期内,由于PAM4的电压等级比NRZ高了两个,即眼图中黑色的区域“眼睛”部分更多、更小了,从而带来了更低的电压裕度和更高的误码率,使得在设备中保证信号完整性成为了一个非常关键的难题。

图2:PAM4调制信号

考虑到PAM4是确保PCIe?6.0达到64GT/s数据传输速率的关键,为此,PCIe?6.0采用了前向纠错技术(FEC)。FEC本质上是一种算法技术,可以在数据传输链路中确保所有信号的完整性。同时,FEC技术的采纳还改变了数据流控制单元的情况,要求开发人员也必须针对数据包本身的大小做出调整和改变。

PCIe?6.0之前的几代规范采用的是可变大小的数据包,但由于FEC技术的采纳,PCIe?6.0必须采用固定大小数据包(FLIT),以更好地保证FEC技术的实现和操作。

此外,考虑到数据传输速率的上升和PAM4技术本身会增加设备的功耗,每一比特数据传输造成的单位数据能耗也会增加。为了减少整体系统的能耗,PCIe?6.0采用了颠覆式的L0p模式,其本质是通过动态的信道分配,允许将每个通道进行封闭或者打开来实现系统性的节能。

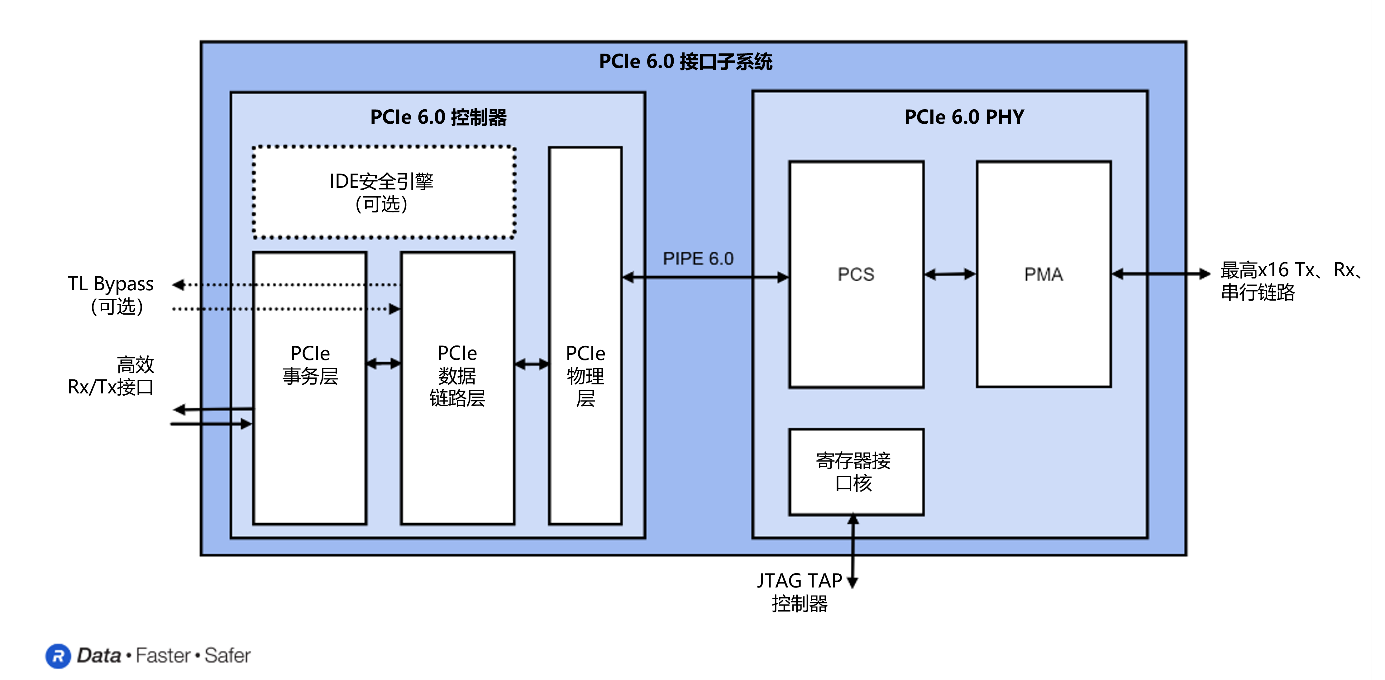

完整接口子系统

Rambus?PCIe?6.0接口子系统的数据传输速率高达64GT/s,并且经过全面优化,可满足先进异构计算架构的需求。该子系统中的PCIe控制器具备完整性和数据加密(IDE)引擎,专门用于保护PCIe链接和通过它们传输的重要数据。另外在PHY方面,它还提供对CXL?3.0的全面PHY支持,支持缓存一致性内存共享、扩展和池化的芯片级解决方案。

图3:Rambus?PCIe?6.0接口子系统(图源:Rambus)

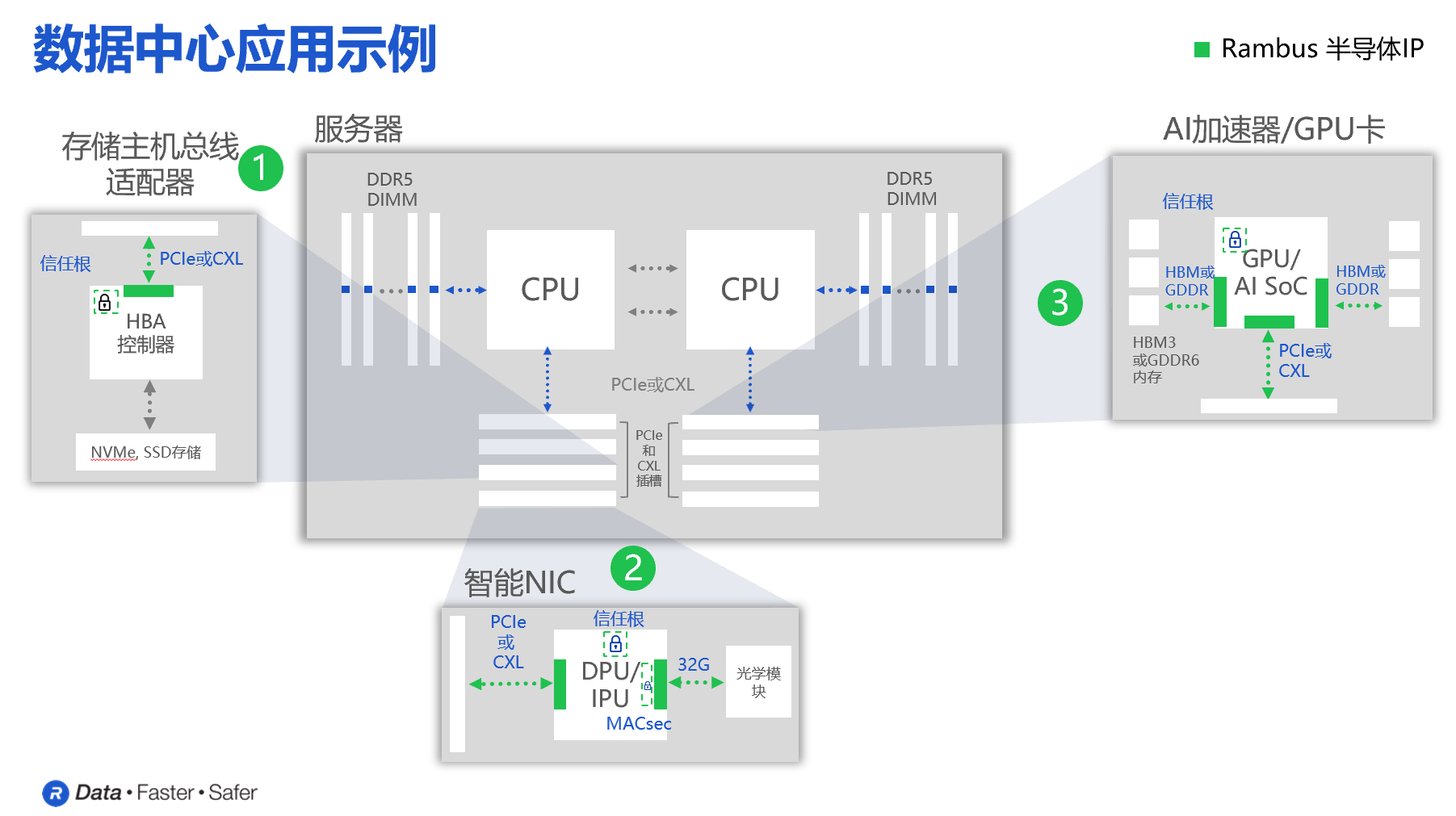

图4是PCIe?6.0接口子系统在数据中心中的应用案例。可以看到,每个示例都有一个存储主机总线适配器、一个智能网卡和一个AI加速器或GPU卡。PCIe?PHY和控制器的组合提供了一个成熟的接口,可以从服务器主板上的PCIe插槽和物理接口连接到控制器芯片上,而且PCIe或CXL接口都经过了硅验证,不会增加设计复杂性。更重要的是,PCIe?6.0子系统还支持包括HBM、GDDR内存PHY和控制器在内的高性能内存和安全解决方案,从而为系统设计人员提供全套完整IP。

图4:PCIe?6.0接口子系统在数据中心中的应用案例

在谈及PCIe?6.0和CXL?3.0之间的关系时,Matt?Jones说这两种技术之所以经常被联系在一起,是因为CXL?3.0协议是建立在PCIe?6.0电气接口之上的,两者拥有共同的电气特性,以确保现有的PCIe硬件、基础设施可以重新应用于CXL。对数据中心来说,同时支持PCIe?6.0和CXL?3.0意味着具体应用在数据中心的灵活性和连接性会得到大幅改善与优化,因为PCIe无论是用于专门的数据传输,还是其他应用场景,都可以带来更好的闪存一致性,也可以与前代CXL?2.0/3.0版本实现无缝集成。

他预测PCIe?6.0的市场采纳时间会在2025年,但从PCIe?5.0过渡到6.0的时间可能比之前几代标准的迭代时间都要更短,尤其是在企业和数据中心数据流量持续爆炸式增长的情况下。

责编:Lefeng.shao