如何在高速信号中降低符号间干扰

【导读】可能影响 PCB 信号完整性的问题列表很长,但在高速通道中特别应该诊断的一种问题是:符号间干扰。这种特定的信号完整性问题涉及比特流中信号之间的干扰,就像其名称所示。那么,是什么导致了这种信号完整性问题?如何减少符号间干扰?

本文要点:

· 即使进行了完美的阻抗匹配,所有传输线也都会存在某些信号完整性问题。

· 由于损耗、色散和寄生组件而经常出现的一个问题是符号间干扰。

· 这种信号完整性问题会导致比特流中的错误,但谨慎的通道设计和驱动器/接收器选择可以有效减少错误。

可能影响 PCB 信号完整性的问题列表很长,但在高速通道中特别应该诊断的一种问题是:符号间干扰。这种特定的信号完整性问题涉及比特流中信号之间的干扰,就像其名称所示。那么,是什么导致了这种信号完整性问题?如何减少符号间干扰?

这个问题通常在电信环境中讨论,但是在 PCB 中也会出现类似的效应。虽然我们永远无法完全从 PCB 中消除信号完整性问题(包括符号间干扰),但可能可以将符号间干扰减少到在典型测量中不会被注意到的程度。本文将讨论如何在高速通道中减少符号间干扰。

1. 什么导致符号间干扰?

符号间干扰是与数位比特流或用于信号标准(如PAM-4)的脉冲流有关的问题。所有有限带宽信道都将显示符号间干扰,而每个电气通道都是到某个高频率的有限带宽。

此信号分析仪测量结果显示了极端的符号间干扰

当数字信号流被接收器读取时,其中一个信号会干扰后续的信号,这种现象被称为符号间干扰。

电信系统,特别是无线系统

符号间干扰通常是由于信号的副本以不同的时间到达接收器所造成的多径效应引起的。就算是对于具有互连和数位位元流的松散布线 PCB 而言,也可能存在符号间干扰问题。

数位信道

位元串流可能会出现一些问题,导致符号间干扰,包括:

· 轻微阻抗不匹配引起的反射

· 相位失真引起的拉伸脉冲(由基板中的色散引起)

· 接收器输入处看到的慢脉冲响应(由负载电容引起)

· 极端的抖动,平均抖动时间与信号的UI相当(这种情况很少见)

符号间干扰可能听起来有点玄乎,但在时域波形中很容易被发现。尽管它是由频域问题(有限带宽)引起的,但在时域中可以很容易地看到它。

2. 诊断符号间干扰

符号间干扰可以在眼图中看到,如下图所示。只要在 PCB 上放置测试夹具,大多数高带宽示波器或数字信号分析仪都可以用来收集此测量数据。

眼图显示符号间干扰

一个完美的眼图会有完全重迭的信号,没有任何抖动(水平上升时间变化)或噪声(信号电平变化)。在上面的图像中,当我们看到波浪状的信号行为重迭在高电平和低电平之间时,就会出现符号间干扰。抖动表现为信号上升时间的水平变化。

3. 在 PCB 板层级上如何减少符号间干扰

在上述清单中的四个要点中,只有前三个非常常见。关于第四点有关抖动的问题,由于功率稳定性的微小变化,总会存在一些抖动。然而,类似 UI 一样巨大的抖动并不常见,除了很可能是高 PDN 阻抗之外的多个问题也导致了非常大的抖动。

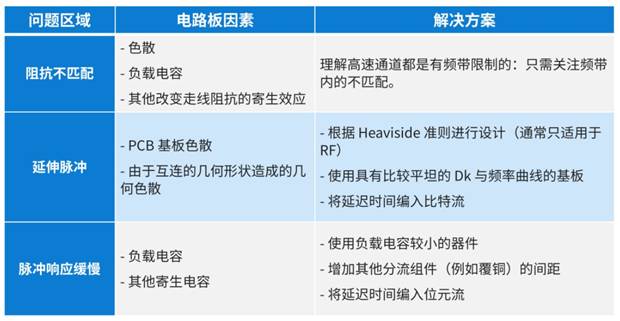

如果要减少符号间干扰,需要着重于三个方面:阻抗不匹配、色散和缓慢的脉冲响应。以下表格概述了一些方法:

选择更少色散的 PCB 层压板和具有更小负载电容的组件等解决方案只能解决部分问题。对于高数据速率信道,最好的解决方案是确保极其精确的阻抗匹配并添加延迟时间。编程延迟到位元流中的解决方案将降低总数据速率,但也会降低误码率。

对于阻抗不匹配,请记住——

我们只需要关注一定范围内匹配阻抗(通常是几个GHz)即可。

还有两种方式可以强制接收器完全忽略由符号间干扰引起的信号电平的干扰 UI 变化,即遵循 Nyquist ISI标准并使用均衡技术。

Nyquist ISI 标准

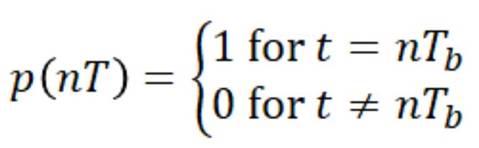

有一种特定的取样率可以在接收器组件中使用,以便恢复的信号完全不受符号间干扰的影响。当接收器读出具有以下特性的数字脉冲流时,就可以满足Nyquist ISI 准则:

Nyquist ISI 标准

在这里,Tb 是数据流的位元率。这个方程式表明,当接收机恰好以比特率进行采样时,只要比特波形在任何其他采样时间都为0,它始终会准确锁定到所发送的位的真实值。通过精确地塑造所传输的波形,可以实现这种性质,需要使用脉冲整形滤波器。

均衡

采用均衡化方案,如分布反馈均衡化,旨在通过估算算法恢复信号质量。这将理想地消除可能叠加在接收信号上的符号间干扰或其他噪声。但是,均衡化不是只需“添加”到组件中即可。它是使用特定电路实现的,该电路内置于组件中。新一代 DDR 和 PCIe 正是在接收端使用均衡化,我们可以期待在未来其他信令标准的下一代中更加标准化。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

使用互补PWM、击穿和死区时间的 H 桥直流电机控制

通信 | 欧洲数字信号干扰器项目

CMOS图像传感器简介

触摸屏与按钮界面设计:电容式和电阻式触摸屏和触觉

Qi充电获得亟需的安全性能提升