摩尔定律走到尽头后,厂商们开始卷封装了

我们总能从各种渠道看到硅片的模样,那散发着五彩光芒的硅晶圆仿佛在向世界诉说着埋在晶圆表面下面那几十亿个晶体管的故事。然而我们日常看到的芯片并不是这样子的。它们有的连接着密集的银白色针脚,有的就是一块纯黑色的方块一样趴在PCB板上。其实芯片原本的样子没有变,它们只是被“放”在了保护壳里。放在保护壳里的这个过程,就是芯片封装。

别小看封装这个过程,它与芯片在最终使用阶段时的体积大小和稳定性息息相关。尤其是目前芯片制程逐渐达到技术瓶颈,摩尔定律已经不能完全描述集成电路技术进步,要想让芯片在工艺层面用更小的体积获得更好的性能,成本逐渐增高。在智能手表、高性能移动设备普及的今天,曾经的“大老粗”芯片早已无法适应今天的使用环境,先进封装或成为绕开摩尔定律的关键。

本文中,与非网将带你认识封装技术的发展,以及了解封装技术的未来展望。

为什么要封装?

其实,要弄懂芯片封装技术的变迁,只要了解为什么需要封装。

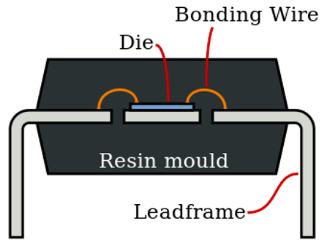

所谓封装就是把集成电路装配为芯片最终产品的过程,对于芯片来说,封装是必须的,也是至关重要的。

晶片需要保护。

芯片电路非常微小也十分脆弱,封装可以有效保护芯片表面以及内部电路免受外界损害以及干扰。此外,封装还可以缓解内部芯片与外部基板之间的热膨胀系数不同导致的应力,用来防止芯片损坏。

芯片与基板之间需要建立电气连接。

芯片对外接脚往往是亚微米级别的,而外部引脚可达上百微米,封装在这里起着由小到大、由难到易、由复杂到简单的变换作用,从而可使操作费用及材料费用降低,而且能提高工作效率和可靠性。

芯片需要标准化、规格化。

标准化的芯片,有着固定的尺寸、形状、引脚数量等参数,便于配合印刷电路板,且生产设备通用,可进行流水线制造。

总的来说,芯片封装有着保护芯片,连接基板,标准化生产等优点。封装技术的迭代也基于这几点进行技术革新。

芯片封装,从“毛毛虫”到“小而美”

从应用的角度看,好的封装技术可以实现更小的体积,更快的速度,以及更多的触点。早期封装的变化过程,就是体积的变小史。

集成电路刚刚诞生的六七十年代,人们对于芯片的印象往往是宽大的引脚,细长的形状,其实这就是芯片最早的封装方式,即DIP(Dual In-line Package)双列直插式封装,绝大多数中小规模集成电路都采用这种封装形式。它通常采用长方形外形,两侧有并排的金属针脚。最早的DIP包装元件是由飞兆半导体(Fairchild)公司的Bryant Buck Rogers在1964年时发明,首个元件有14个引脚,采用此类封装的半导体元件可以接在印刷电路板电镀的贯穿孔中,或是插入在DIP插座(socket)上。早期芯片,例如8086、8088等CPU都采用了DIP封装。不过这种技术密度、频率难以提高,无法满足高效自动化生产的要求,且芯片面积与封装面积的比值较大,体积也很大。

DIP封装

图源 | 维基百科

更多的触点永远是芯片封装技术追求的目标。80年代开始,DIP封装的两排针脚已经不能满足芯片与外界交流的需求,SMT表面贴装时代到来让芯片封装有了更多发挥空间。SMT技术是一种将无引脚或短引线表面组装元器件安装在印制电路板的表面或其它基板的表面上,通过再流焊或浸焊等方法加以焊接组装的电路装连技术。SMT工艺包括丝印、点胶、贴装、固化、回流焊接、清洗、检测等步骤。相比前代封装技术,SMT组装密度更高,体积更小,重量更轻。

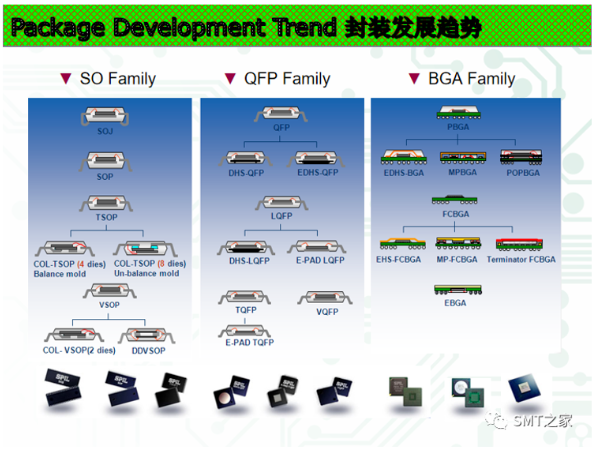

SOP(Small Out-Line Package小外形封装)封装是一种常见的表面贴装形式,引脚从封装两侧引出呈海鸥翼状或L状。SOP与DIP封装的外表很像,从功能上也是没有区别的,只是在芯片焊接阶段,由于SOP引脚小,焊接难度会比DIP大一点,不过SOP的价格相比DIP也便宜一点。SOP封装还逐渐派生出了许多其他的封装类型,例如SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、TSSOP(薄的缩小型SOP)等。

QFP封装,中文含义叫方型扁平式封装技术(Quad Flat Package),该技术实现的CPU芯片引脚之间距离很小,引脚很细,一般大规模或超大规模集成电路采用这种封装形式,引脚中心距离有1.0mm、0.8mm、0.65mm、0.5mm、0.4mm、0.3mm 等多种规格,总数一般都在100以上。QFP及其他派生封装技术的可以更有效的利用空间,高度与体积都缩小了很多。

90年代面积阵列封装出现。PGA、BGA等封装技术逐一应用,在缩减体积的同时提高了系统性能。

PGA(Pin Grid Array)插针网格阵列是一般用户很熟悉的封装形式,很多老款的CPU都采用PGA封装,其最大的特点就是背面布满针脚。这种类型的封装底部布满针脚,使用时需要将整块芯片放置于对应的卡座内,不过缺点很明显,就是容易“断脚”,后来逐渐被针脚在PCB板上的平面网格阵列封装LGA(Land grid array)替代。

BGA改良自PGA。BGA(Ball Grid Array)球栅阵列封装是一种表面黏着封装技术,相比DIP以及QFP封装技术,BGA可以容纳更多的接脚,整个装置的底部表面可全作为接脚使用,而不是只有周围可用,比起QFP等周围限定的封装类型还具有更短的平均导线长度与更好的高速效能,与TSOP相比,BGA具有更小的体积、更好的散热和电学性能,并极大地提高了每平方英寸的存储容量。因此由该技术实现封装的CPU信号传输延迟小,适应频率可以提高很大。和PGA相比,BGA一般直接焊接在PCB板上,拆卸焊接需要专用的BGA修复台,但价格也比PGA更便宜。

不同封装的区别

图源 |SMT之家

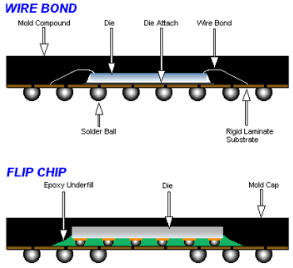

从最开始的DIP封装到CPU使用的BGA、LGA型封装,我们可以明显的看到芯片的体积在逐步缩小,与外界交换信息的针脚也在增多。然而这些封装技术都不能摆脱wire bond的限制,也就让芯片的功率上限较低,也难以承受超高频率的运算性能。21世纪的新封装技术将解决这个问题。

封装,不止关注体积

进入21世纪后,移动设备对于芯片的需求逐渐提升。芯片制程沿着摩尔定律快速发展,这同时也对封装技术提出新的考验。为了进一步提升芯片的整体性能,倒晶封装技术Flip Chip出现(或称覆晶封装、倒装芯片、controlled collapse chip connection、c4等)。以往封装是将晶片置放于基板(chip pad)上,再用引线焊接(wire bond)将晶片与基板上的焊盘连接。Flip chip是先将晶片连接到凸块(bump),然后将晶片翻转过来使凸块与基板(substrate)直接连结而得其名。Flip Chip与传统wire bond封装技术相比,晶片与基板的互连形式要方便的多,芯片焊盘位于芯片正下方,因此与基板之间连接路径较短,能显著提高电气性能,更提高了I/O数量;芯片底部区域阵列焊接点的密度也更高,因此整颗芯片的尺寸能显著缩小。此外,晶片倒装后没有引线的限制,芯片整体高度更低,外部散热也可以直接作用于晶片之上。

Flip chip技术与其他封装,例如BGA封装技术并不是相互独立的,应用Flip chip技术的BGA同样能有效降低芯片体积。

Flip chip

图源 | integra报告

Flip chip有着尺寸、I/O密度、传输性能、散热能力以及生产效率等诸多优点,不过先进封装也有更“先进”的问题需要解决。

Flip chip技术面对的最大难题就是解决芯片翘曲,这在芯片超薄化后成为影响封装良率的关键问题。Flip chip的组装过程需要将芯片上的焊点与基板上的焊盘进行对位,然后使用回流焊工艺在芯片和基板焊盘间形成焊球,再在芯片与基板间的空隙中填充底部填充胶(点胶),最终实现芯片与基板间的电气连接。因此这个流程的第一步,焊点与焊盘的对应十分重要。若芯片产生过大的翘曲会在组装过程中导致锡球无法对接,出现开路。目前,采用新材料做基板可以有效降低热膨胀系数,减小翘曲度。此外采用铜柱技术(CopperPillar)也可以进一步缩小焊点间距。

随着各种智能设备小型化的发展,要求作为终端的传感器更便携化、多功能化。因此,将更多功能集成于单个芯片内成为降低体积、提升性能的高效方式。因此,叠层3D封装出现了。

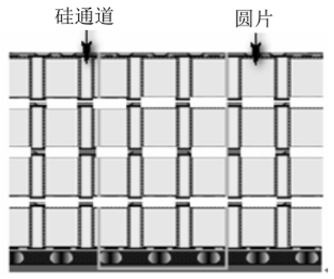

目前,芯片叠层共有三种形式:芯片与芯片的堆叠(Die to Die,D2D),芯片与晶片的堆叠(Die to Wafer,D2W),晶片与晶片的堆叠(Wafer to Wafer,W2W)。

D2D利用传统的引线连接技术,将芯片在垂直方向上堆叠起来进行封装,应用传统的封装技术即可解决。D2W则需要Flip chip技术来连接上下两层。W2W的上下两层之间通过直径在10微米以下的硅通道相连接,这种技术也称为TSV(Through silicon via)。与其他技术不同,TSV能够使芯片在三维方向堆叠的密度更大、外形尺寸更小,并且大大改善芯片速度和降低功耗,是目前3D芯片的主流发展方向。

TSV堆叠

图源 | 中国集成电路报告

除了垂直封装技术外,在同一个封装腔体内堆叠多个3D封装也是一种技术方案。PIP(Package in Package)封装内封装逐渐流行。目前该项技术主要用于SD卡、XD卡等储存芯片的封装上。

先进封装,超越摩尔定律的关键赛道

目前,半导体业界逐渐意识到了制程不会无限缩小下去,晶体管也不可能无限增加下去。摩尔定律首先是一条经济上的定律,然后才是工程科学方面的定律。人们专注于提高芯片制造技术达到瓶颈之后,与之对应的封装技术发展也同样慢了下来。封装还是要回到原点,也就是文章开头所提到的:为什么要封装?什么才是好的封装?

好的封装,不仅能保护芯片,还具有更小的体积,以及更好的电气性能。因此,封装的发展面临了三条路可以选择:More Moore,More than Moore,Beyond Moore。

More Moore是沿着摩尔定律这条路一直走下去,钻研更精细、更先进的封装方案,这也往往面临着高昂的制造成本,也就是SoC的发展路径。More than Moore则是绕过摩尔定律,采用其他技术达到同样的更小、更先进的目标。Beyond Moore则需要超越现有芯片体系,或许只能在非硅基半导体上实现。

就目前来说,More than Moore是一项最经济也最便捷的选择。SIP(System In a Package)系统级封装是目前芯片封测厂商的主流之选。它是一种是将多种功能晶圆,包括处理器、存储器等功能晶圆根据应用场景、封装基板层数等因素,集成在一个封装内,从而实现一个基本完整功能的封装方案。

SIP封装

图源 | 知乎

SIP与SoC对比,两者均将一个包含逻辑组件、内存组件,甚至包含被动组件的系统,整合在一个单位中。而SIP则是从封装角度出发,利用并排或叠加的方式,将不同制程的芯片集成在一起。我们知道,越高的制程也拥有越高的制造成本,SIP可以仅在关键模块上使用高端制程,例如CPU、GPU等,在其他模块上,例如WIFI、触控模块上使用成熟制程,这将极大的降低制造成本。

此外,SIP还将绕过PCB板载体,解决因为PCB自身的先天不足带来系统性能遇到瓶颈的问题。存储芯片和处理器之间也能做到更快速的数据交换,真正做到存算一体化。

写在最后

芯片封装,已经从刚起步时仅作为保护作用的外壳,成为今天提升芯片电气性能,绕过摩尔定律发展的关键。后摩尔时代,芯片封装技术将成为解锁未来半导体技术的关键。

1