除了EUV,还有一种光刻机好像也很有戏(上)

今年进博会期间,我们特别采访了佳能——采访围绕的核心自然是佳能的光刻机。当时佳能提到一种名为纳米压印(nano-imprint)的光刻技术。这是一种不同于现在我们所熟知的基于EUV极紫外光光源的光学曝光的技术方向。

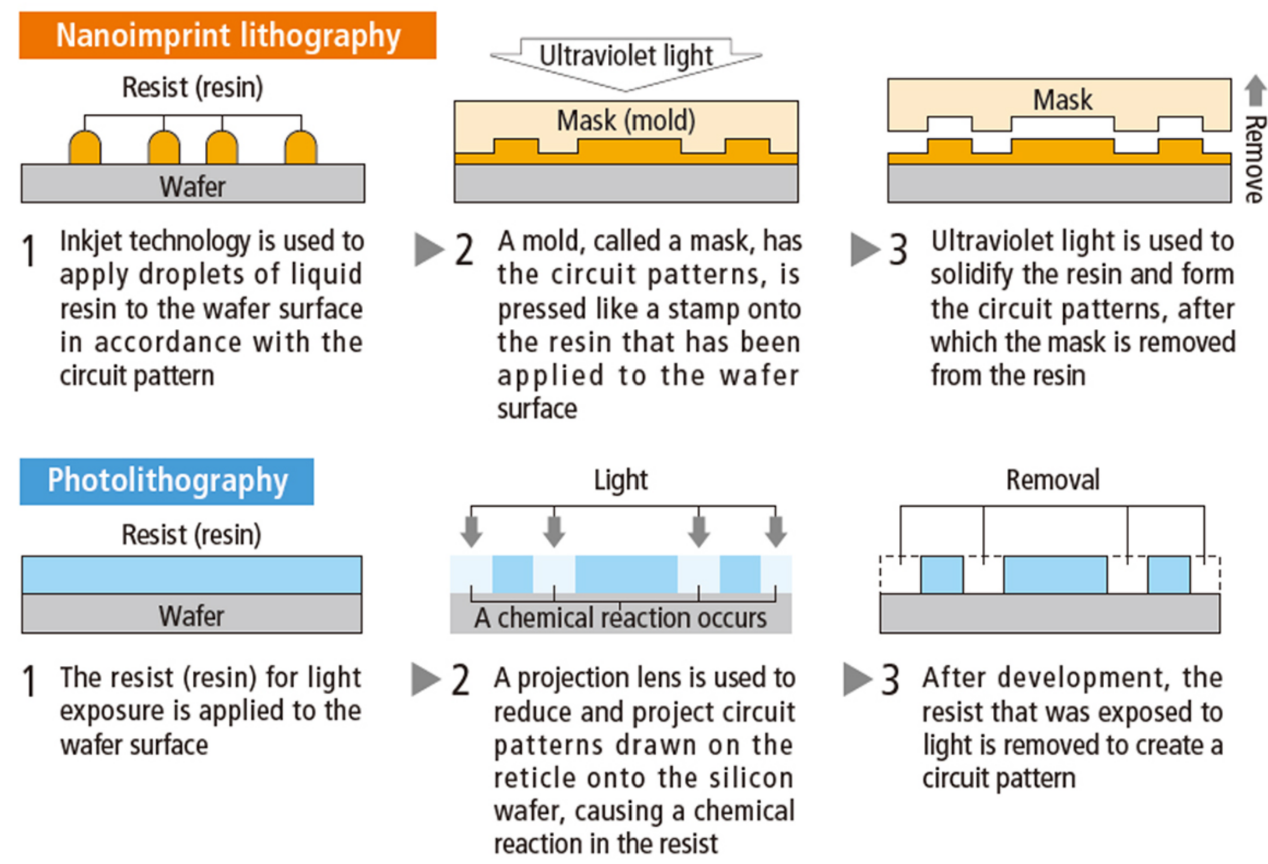

佳能说这种技术“类似于盖章,没有复杂的光学元器件”,不是在图案mask掩模板之后做微缩曝光,而是一种等比例技术,“一次压印成型,不像传统光刻会用到SADP/SAQP等复杂工艺”。

前不久TechInsights发了一篇光刻技术当前发展现状的eBook,提到除了EUV光学曝光以外,lithography技术三个可能有前途的方向,包括NIL(nano-imprint?lithography)、DSA(direct?self-assembly)、EBL(electron?beam?lithography)。NIL就是佳能所说的纳米压印。

这篇文章,我们就来聊聊这种不同于常规光学曝光路线的纳米压印。实际上我们认为nano-imprint?lithography并非光学曝光,所以理论上叫“光刻“是不大合理的。不过似乎行业有这样的约定俗成,本文会将所有半导体制造流程中的lithography称作“光刻”(台湾习惯上将其译作“微影”其实会更妥帖)。

?

佳能还真是最大投注者

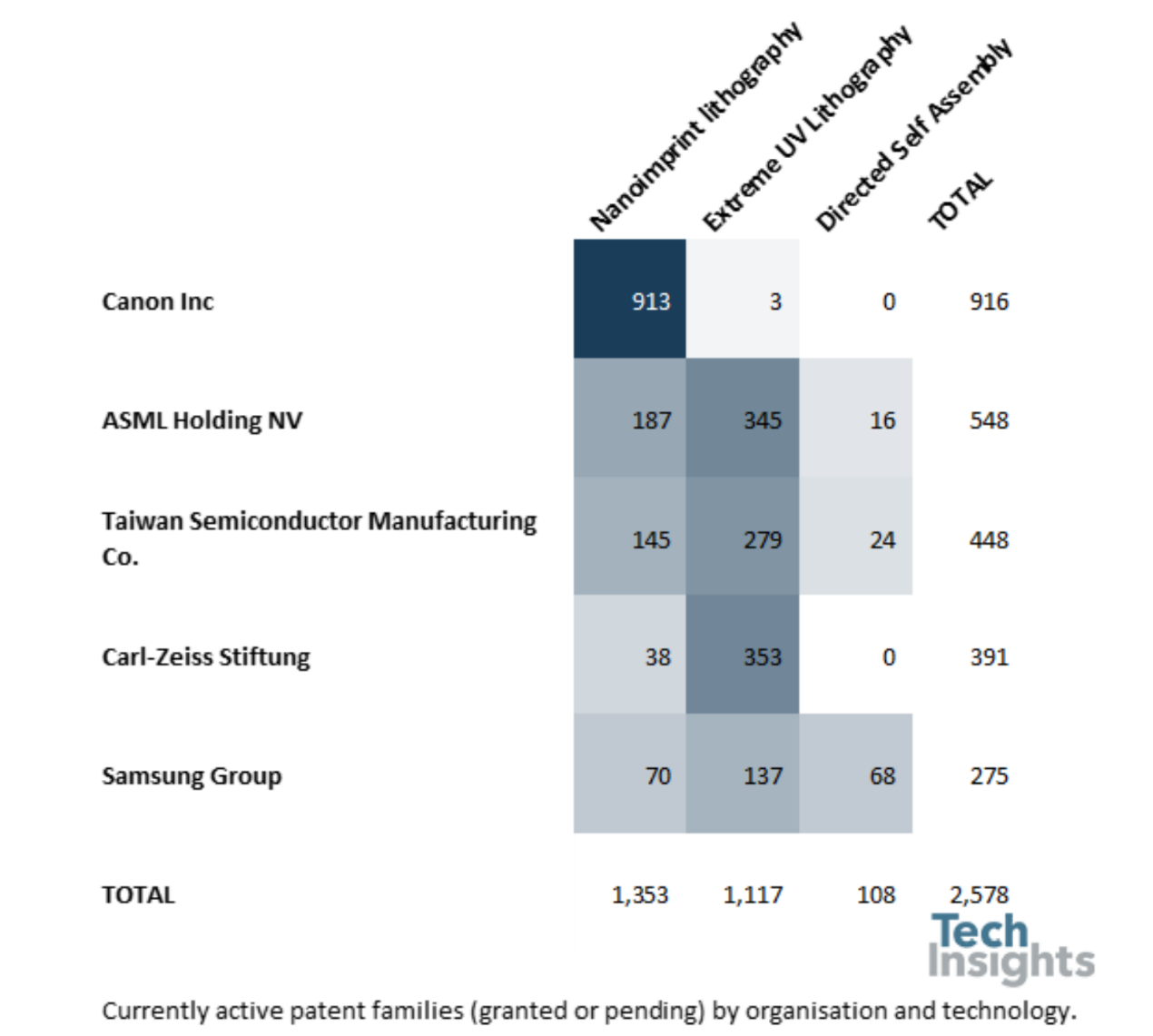

TechInsights和Cipher合作总结了光刻技术主流市场参与者,在几个主要光刻方向上的专利拥有量。佳能毫无疑问是NIL纳米压印技术方向投注最多的——当然这与其此前收购MII有关;没想到的是,ASML和台积电在NIL上其实也还是有相当投入的。

来源:LITHOGRAPHY: Gatekeeper to Technological Independence and Advancement,?TechInsights

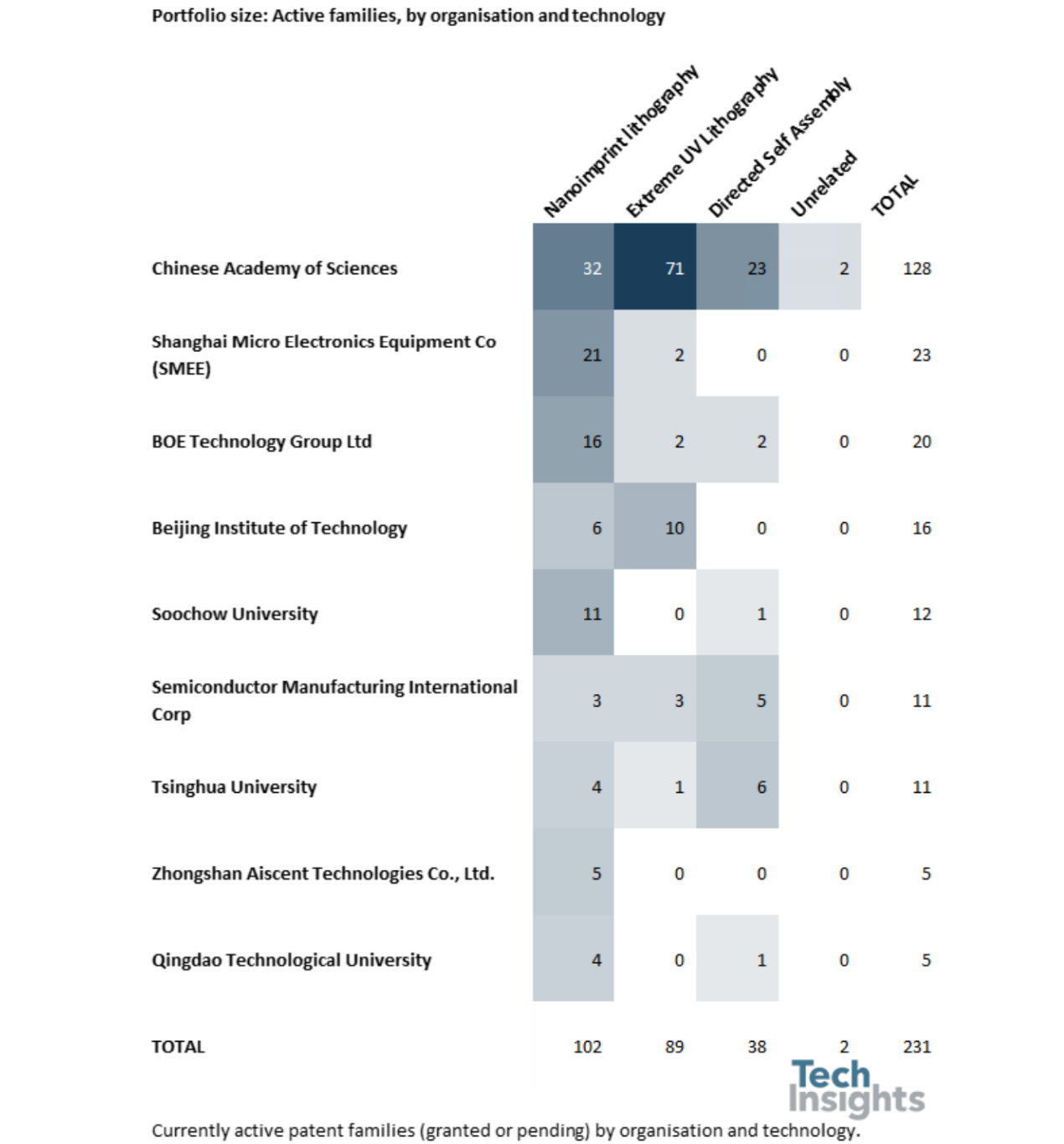

另外再附上国内部分参与者在这几项技术上的专利储备情况,此处不做过多评论。而从全球和国内在光刻技术方面的技术储备来看,纳米压印虽然说不上主流-或者说在半导体IC制造上还并不曾全面崭露头角,也远不及EUV光学曝光那么知名,却似乎也有前途。

来源:LITHOGRAPHY: Gatekeeper to Technological Independence and Advancement,?TechInsights

此前佳能就告诉我们,其纳米压印设备仍在“做量产评估,十几纳米已经成功实现”,“我们相信将来是能够做到的。”

前不久佳能就宣布准备在日本建造新工厂,以提升半导体光刻设备的产能。计划中扩产的工厂也会造KrF和i-line设备。而纳米压印设备则是佳能寄予了厚望、要在半导体制造领域开启新时代的产品。在今年第三财季面向投资者的会议上,佳能也特别提到了“尖端纳米压印光刻设备”。

佳能的新厂位于东京以北的宇都宫,投入预计超过500亿日元,正式运营大约会从2025年开始。铠侠(Koxia)届时计划开始用纳米压印技术,进行NAND闪存的量产——这件事倒并不让人意外,因为从有关纳米压印的历史新闻来看,东芝(铠侠前身)一直都是纳米压印在半导体制造领域的最大拥趸。

东芝/铠侠、佳能和DNP(Dai?Nippon?Printing,大日本印刷)此前在纳米压印技术上也做了不少年的合作。DNP?2015年据说是建立了纳米压印模板(template)的商业化生产系统;而东芝是2016年宣布计划用纳米压印来造NAND闪存的。目前这一技术方向的其他设备供应商还包括EVG(Electronic?Visions?Group)、SUSS?MicroTec、Obducat——这几个都是欧洲公司。

佳能原本期望纳米压印于2019年达成规模化量产的,现在看来还是不切实际了些。而其纳米压印设备据说最初装于铠侠的四日市(Yakkaichi)NAND工厂,但目前尚未实现量产。

?

一直在尝试取代光学曝光

从大方向来理解NIL纳米压印技术,可以简单概括为:(1)首先系统基于预定义好的设计,在模板(template)上形成图案;(2)在substrate上涂上保护涂层(resist,不知此处可否直接将其称作光刻胶);(3)然后就像冲压一样,模板对着substrate压上去,就在substrate上形成了图案。

从大方向来看,这样的方案和光学曝光差异还是挺大的,不过似乎压印用到的保护涂层需要用UV光来做cure固化(UV-NIL技术方向),多少也算有点“光刻”的名义吧;而且或许若探究template模板本身的生产过程会更复杂。

如果单说优势的话,纳米压印不需要用到昂贵的光学设备,也不用多次重复曝光,成本是其显著优势。还有个很符合时下热点的优势:节能。此前采访中,佳能就特别提到了纳米压印设备功耗显著低于EUV光刻机。据说前者相比于后者功耗低90%,整体的处理成本少40%,价格相比EUV?scanner更是低了很多。

从Helmut?Schift在nanopedia撰写的资料来看,NIL纳米压印技术最早可以追溯到上世纪70年代,发源自日本NTT,当时就有人申请了UV纳米压印光刻技术专利;不过NIL真正受人关注,是在1996年《科学(Science)》杂志发表报告提到了nanoimprint?lithography这个词,文章由明尼苏达大学Stephen?Chou教授(以及Peter?Krauss和Preston?Renstrom)发表。据说当时这名教授就演示了达成10nm的压印能力,而彼时光学曝光的限制还停留在50nm。

而且在3年之后,Stephan?Chou创办了Nanonex,就搞NIL设备。本世纪初,NIL技术的主要参与者包括有EV?Group、Molecular?Imprints(MII)、Nanonex、Obducat等。这一时期NIL进入实际生产阶段,不过早期并不是针对半导体芯片制造的。

据说NIL在非半导体市场上的发展还不错,且某些领域的应用是真正走向了成熟的,典型的比如LED制造、生物工程(控制细胞生长?)、太阳能电池;在应用于DNA拉伸实验时,NIL达成了<10nm纳米流体通道(nanofluidic?channel)的制造。而在发展过程中,真正坚持把半导体光刻这个应用方向做下去的也变得越来越少,MII是其中之一。

2003年NIL纳米压印是作为下一代光刻技术(NGL)技术备选正式存在于ITRS(International?Roadmap?for?Semiconductors)路线中的;同处在NGL列表中的其他技术方向还包括157nm光刻、EUV光刻、EPL。也就是说,NIL是面向32nm、22nm节点的路线备选技术之一。

虽然我们都知道行业步入22nm节点之时,光学曝光仍然是毫无争议的主流,但NIL在更小的工艺节点上,仍位列ITRS;后续也有观点认为NIL会成为EUV曝光的最有力竞争者。2009年,MII还真的曾规划将NIL技术用于32nm逻辑节点生产制造。但进展也未及预期——据说是因为生产速度慢,而且缺陷率高,资金问题也成为MII发展技术的掣肘。

但NIL纳米压印能坚持至今未被彻底丢弃,大概还是表明其潜在价值的。像157nm光刻、EPL之类的技术就已经在历史长河中相继消失了;即便现在的主流还是193nm浸润式光刻配合多重曝光,以及发展态势相当良好的EUV——对应的7nm、5nm工艺节点都已经存在于我们的日常生活中。

2014年,佳能收购了MII。实际在收购之前,MII就向东芝出货了纳米压印设备——东芝很早就想将NIL用在平面NAND闪存制造上。不过似乎193nm光刻和多重曝光就能将NAND单元尺寸从120nm缩减到1xnm节点;而且到这个节点,原有工艺就很难再实现存储单元和浮栅(floating?gate)的微缩。

NAND很快向3D化发展,东芝对于NIL系统的应用也有了转向。大约5年前,东芝说非易失性存储器件的光刻需求,正从更高分辨率走向更低的成本,所以计划在3D?NAND时代应用NIL,包括针对SCM(存储级内存)。

?

纳米压印准备就绪了吗?

在3D?NAND技术上,东芝选择了和西数合作;此外SK海力士开发NIL技术也与东芝达成了一些协议。其实对于3D?NAND而言,光刻这个步骤的技术地位已经不及从前了。制造3D?NAND技术挑战主要转向了沉积和蚀刻。

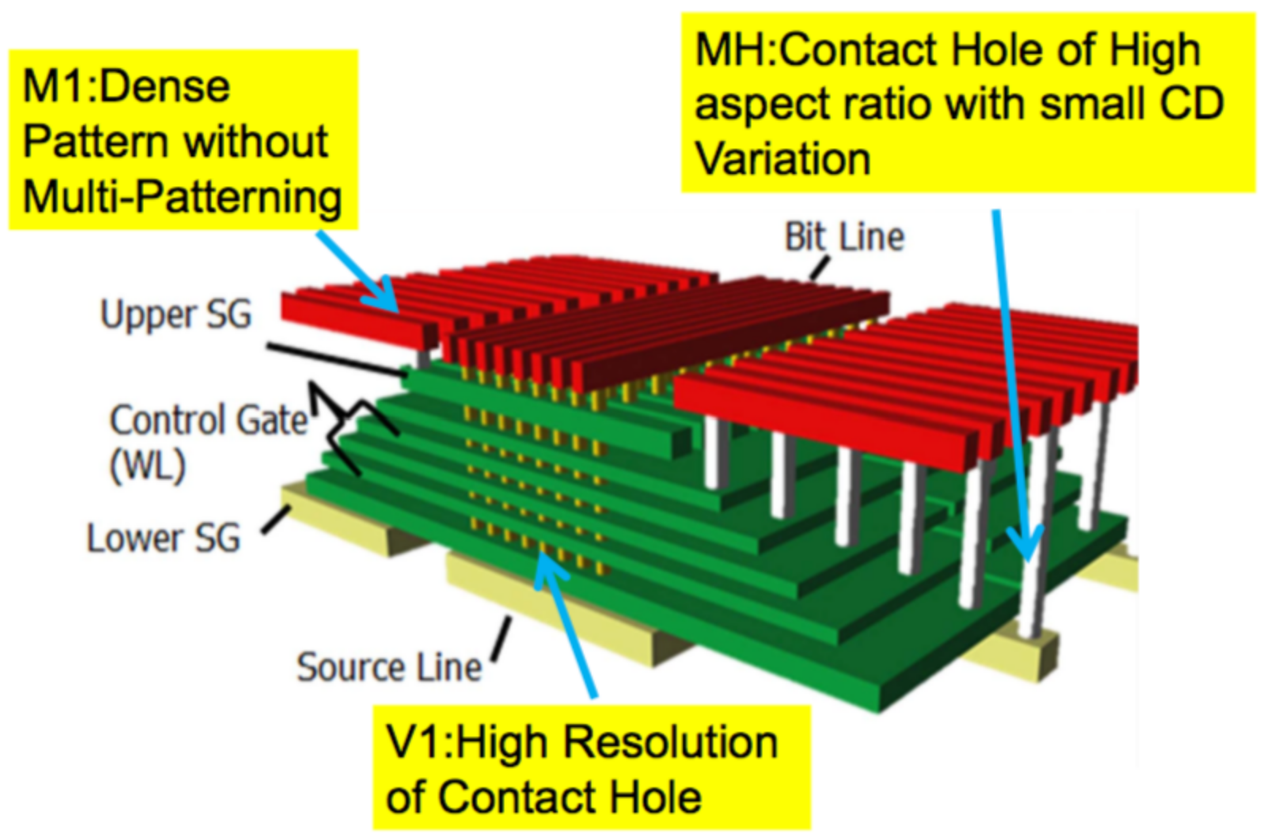

东芝主要是期望在3D?NAND的contact?hole?patterning上采用NIL,还有其他部分如下图。相比于光学曝光需要SADP/SAQP,NIL减少了EPE(edge?placement?error)的发生,并且预期中成本也能降低。

其实前些年就有报道说,NIL可能有戏了(或者每隔几年就会有这样的说法)。NIL本身的确面临着几个主要技术挑战。首先是template模板的缺陷率控制问题,否则就会在substrate上不停造成重复的缺陷。

另外overlay也一直是个问题?–?也就是scanner对齐、打印各个层的精度问题。似乎2018年,佳能把MMO(mix?and?match?overlay)做到了<3.5nm,同等精度差不多对存储器件生产而言是足够的。还有就是产能吞吐问题……下篇会对NIL面临的技术挑战做更详细的解读。

虽然NIL技术进展见诸报端的新闻并不多见,绝大部分还都不是和半导体制造相关的进展。但值得一提的是,在中美贸易摩擦市场环境下,NIL技术所处的位置显得很特别——尤其当中国使用EUV技术屡屡受阻的情况下。Asia Times前不久报道说,佳能未来的新工厂上线,则大量输出会面向中国。虽然还是要等后续的实物问世。

Helmut?Schift在介绍NIL的paper中,致谢部分提到NIL工艺技术的发展是许许多多的研究人员、工程师、技术专家共同参与的结果,他们开发出了工具、材料、工艺方案和应用。“我们很幸运NIL并不是为某个小众研究应用打造的,也不是仅仅专为半导体IC芯片大规模量产所准备的”——虽然我们还是更关注它在IC制造上的发展潜力。

本文的下篇会尝试更详细地去谈纳米压印NIL的工艺流程,及其主要技术挑战。

责编:Illumi