规避“标准有国界”,中国发布原生Chiplet技术标准

近几年,作为延续摩尔定律的先进封装技术成为半导体产业的热点技术。继2021年Chiplet标准立项之后,在12月16日“第二届中国互连技术与产业大会”上,首个由中国集成电路领域相关企业和专家共同主导制定的《小芯片接口总线技术要求》团体标准正式通过工信部中国电子工业标准化技术协会的审定并发布。这是中国首个原生Chiplet技术标准,对延续“摩尔定律”、突破先进制程工艺限制具有重要意义。

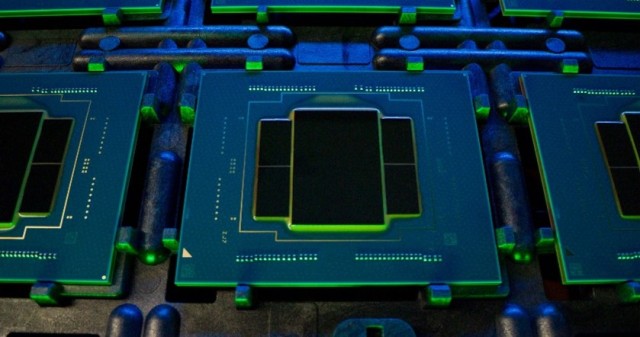

摩尔定律放缓、chiplet势头渐盛

Chiplet一般指芯粒,也指“小芯片”,即把预先制造好的、具有特定功能的、可组合集成的芯片。芯粒是不同功能芯片裸片的拼搭,某种意义上也是不同IP的拼搭。实际上,Chiplet这种技术源自2015年由Marvell创始人周秀文在ISSCC?2015上提出的MoChi(模块化芯片)架构概念。而AMD率先将chiplet应用于商业产品中。

而Chiplet技术逐渐被各大芯片巨头重视的重要原因在于摩尔定律放缓。按照摩尔定律:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。但近些年,由于摩尔定律已经放缓,特别是5纳米、3纳米芯片工艺之后,芯片性能并未提升一倍,成本反而直线上升,先进芯片工艺渐呈难以为继的态势。为此,全球芯片企业开始从先进芯片封装技术上寻找性能和成本的平衡点,也成为很多芯片产业链企业的共识。

Chiplet有哪些优势?主要体现在:一是降低成本,比如The?Linley?Group的白皮书《Chiplets?Gain?Rapid?Adoption:Why?Big?Chips?Are?Getting?Small》中直接提出,Chiplet技术可以将大型7nm设计的成本降低高达25%;在5nm及以下的情况下,节省的成本更大。

二是提高芯片制造的良品率。资料显示,芯片的良品率与芯片的面积有关,随着芯片面积增大,良品率会下降。通过Chiplet设计将大芯片分成更小的芯片可以有效改善良率,同时也能够降低因为不良率而导致的成本增加。

三是降低设计的复杂度和设计成本。因为如果在芯片设计阶段,就将大规模的SoC按照不同的功能模块分解为一个个的芯粒,那么部分芯粒可以做到类似模块化的设计,而且可以重复运用在不同的芯片产品当中。这样不仅可以大幅降低芯片设计的难度和设计成本,同时也有利于后续产品的迭代,加速产品的上市周期。

简单来说,Chiplet技术能将采用不同制造商、不同制程工艺的各种功能芯片像搭乐高积木般进行组装,从而实现更高良率、更低成本。

来源:Ayar?Labs

来源:Ayar?Labs

近几年,AMD、英特尔、台积电、三星、英伟达等国际芯片巨头纷纷布局Chiplet,?设计样本也越来越多,开发成本下降,加速了Chiplet技术生态的发展。据Omdia报告,2018年Chiplet市场规模为6.45亿美元,预计到2024年会达到58亿美元,2035年则超过570亿美元。

为何要打造中国原生“小芯片”标准?

在谈Chiplet技术标准之前,我们有必要提一下UCIe标准。

由于传统芯片设计阶段涉及的各种IP都有标准,所以厂商无需担心用起来无所可依。然而,在chiplet这个新兴技术领域中,芯片企业可能会涉及到多家同时在做各种功能芯片的各类设计、互连、接口,如果没有统一的标准,市场和生态是做不大的。

为此,今年3月,在英特尔的牵头下,“UCIe联盟”的成立。这个联盟从初始就汇集了几乎所有芯片巨头公司——英特尔、AMD、ARM、Google?Cloud、Meta、微软、高通、三星、台积电,将共同打造Chiplet互连标准,携手推动Chiplet接口规范的标准化。目前,一些中国芯片企业也加入了UCIe联盟,比如阿里巴巴在8月初成为Chiplet全球产业联盟UCIe的董事会成员。

不过,尽管UCIe联盟旨在打造一个开放的Chiplet标准,但实际上对中国芯片企业的开放程度还存诸多疑问。有专业人士表示,从PCIe到CXL、AIB和UCIe,实现参考设计所需要的技术细节,在Chiplet标准协议根本找不到。实际上,一些标准的细节还被美国相关组织告知不能对中国企业开放。可想而知,在以英特尔、AMD、高通等美国企业主导下,UCIe联盟很难不成为一种政治化的工具。

从2019年华为被美国列入实体清单,到今年10月美国进一步加大对华芯片技术管控,中国芯片企业已经越来越难从国际合作中获得任何有利自身成长与发展的机会。当前,科技竞争已被“武器化”“泛国家安全概念”,如果再次遇到美国升级技术出口管制措施,严重依赖UCIe标准的中国企业必然要陷于美国政府的“视同出口”规定的压制。

当前,在先进芯片工艺制程上,中国企业无法在短期内缩短与国际芯片巨头的差距。如果先进制程技术的供应长期受阻,中国企业可以借助先进封装技术,即通过集成电路互连技术把采用成熟工艺制程的芯片连接在一起,在先进封装技术的支持下,实现或接近实现一个需要采用先进制程做出的芯片性能。

为此,中国需要在“小芯片”技术上打造一个原生的Chiplet标准。2021年5月,中国计算机互连技术联盟(CCITA)在工信部立项了Chiplet标准,即《小芯片接口总线技术要求》,由中科院计算所、工信部电子四院和国内多个芯片厂商合作展开标准制定工作。

今年3月28日,由中国计算机互连技术联盟(CCITA)联合电子标准院,多家企业、科研院所等经过10个月努力共同制订的《小芯片接口总线技术要求》、《微电子芯片光互连接口技术》完成标准草案制定,开始面向社会征求意见。

Chiplet面临的挑战与机遇

据悉,《小芯片接口总线技术要求》描述了CPU、GPU、人工智能芯片、网络处理器和网络交换芯片等应用场景的小芯片接口总线(Chiplet)技术要求,包括总体概述、接口要求、链路层、适配层、物理层和封装要求等。

该标准列出了并行总线等三种接口,提出了多种速率要求,总连接带宽可以达到1.6Tbps,以灵活应对不同的应用场景以及不同能力的技术供应商,通过对链路层、适配层、物理层的详细定义,实现在小芯片之间的互连互通,并兼顾了PCIe等现有协议的支持,列出了对封装方式的要求,小芯片设计不但可以使用国际先进封装方式,也可以充分利用国内封装技术积累。

要指出的是,Chiplet虽然有诸多优势,但仍处于发展的早期,面临着来自互连接口与协议、封装技术以及质量控制等方面挑战。主要体现在:一是Chiplet的封装和互连/接口技术尚缺乏统一的标准;二是裸芯片的质量保障问题;三是散热问题,也是要重点解决的问题,毕竟几个甚至数十个裸芯片封装在一个有限的空间中,互连线非常短,使得散热问题变得更为棘手;四是芯片网络问题;五是供应链重塑问题,在Chiplet模式下,EDA工具提供商、芯片提供商、封测提供商都要有所改变,以适应Chiplet发展的需求。

不过,尽管Chiplet技术还存在一些尚未解决的技术问题,例如缺少标准的互连接口和封装术,包括EDA工具在内的供应链仍需进一步完善等,但Chiplet技术已经在多个应用领域展现出了良好的效能及性价比,也将在一些领域带来新的动力。

芯原股份是中国大陆首批加入UCIe联盟的企业之一。该公司董事长兼总裁戴伟民就曾表示,“Chiplet主要适用于大规模计算和异构计算,其中平板电脑应用处理器、自动驾驶域处理器、数据中心应用处理器将是Chiplet率先落地的三个领域。”

部分国内上市公司Chiplet技术发展概况

| 企业 | 概况 |

| 芯原股份 | 此前已经正式宣布加入UCIe产业联盟,成为中国大陆首个加入该产业联盟的企业。近期被调研时称“是大陆排名第一、全球排名前七的半导体IP供应商,已经成为了大陆首批加入UCIe联盟的企业之一,可能是全球第一批面向客户推出Chiplet商用产品的企业”。 |

| 长电科技 | 公司已于今年6月加入UCIe产业联盟 |

| 华天科技 | 公司称掌握chiplet相关技术。 |

| 通富微电 | 公司已大规模封测Chiplet产品;公司在Chiplet、WLP、SiP、Fanout、2.5D、3D堆叠等方面均有布局和储备。 |

| 寒武纪 | 公司思元370是首款采用Chiplet(芯粒)技术的AI芯片。 |

| 晶方科技 | Chiplet技术目前是行业发展的趋势之一,公司在研究该技术路径的走向,并与合作伙伴共同寻找合适的产品应用。 |

?

责编:Jimmy.zhang