SRAM缩微化大大减缓???或影响台积电3纳米及以下工艺

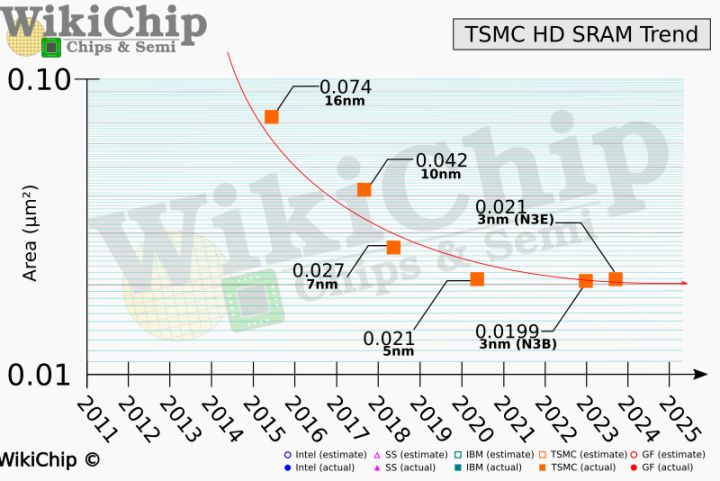

当前,芯片缩微化已经逐渐逼近物理极限,但先进芯片工艺的探索却从未停止。在先进芯片工艺上,保持技术领先一直是台积电成功的关键因素,比如台积电5nm工艺曾拥有世界上最小的SRAM单元(0.021平方微米)。然而,近日WikiChip发布的一份报告提到,台积电在SRAM方面的微缩速度已大大放缓,且认为SRAM单元缩微化减缓将对3纳米及以下的芯片工艺带来很大影响。

一直以来,终端应用不断对半导体技术提出更高的要求,也在很大程度上推动了先进芯片工艺的进步,特别是高性能计算(HPC)、人工智能以及5G通信等,都要求在有限的功耗下实现最高的性能。为此,台积电、三星两大全球领先的芯片代工厂商已经把芯片工艺推动至3纳米,而且也推出了3纳米以下芯片工艺的计划。但从最近几年芯片缩微化来看,SRAM密度明显要慢于芯片逻辑密度,也必然对未来更先进的芯片工艺进展带来更大的挑战。

图片来源:WikiChip

实际上,在5纳米工艺上,台积电已经遇到SRAM缩微化减缓的情况。台积电在IEDM?2019上发布了其5nm工艺,其在5nm工艺中使用了十几张极紫外(EUV)掩模,每张EUV代替三个或多个浸没掩模以及采用高迁移率沟道(HMC)的以获得更高性能。其5nm工艺自2019年4月起投入风险量产,并于2020年第一季度实现全面量产。

不过,FinFET晶体管尺寸的量化一直是主要挑战,并迫使高密度6T?SRAM单元中的所有晶体管仅能使用一个Fin。台积电通过设计工艺协同优化(DTCO)对设计进行了优化,以提供高性能和高密度以及高产量和可靠性。

值得一提的是,数据显示,2017年至2019年的SRAM单元面积缩小速度远慢于2011年至2017年的速度,这表明SRAM单元的微缩速度没有跟上逻辑区域的部分。在IEDM?2019上,5nm工艺的逻辑密度提高了1.84倍,而SRAM密度仅提高了1.35倍。

据悉,SRAM在芯片当中可以充当高速缓存存储器,SRAM微缩越好,在不影响性能和功率的同时就可以为其他单位芯片提供更大的面积,并借此提升芯片的整体性能。而根据近日的WikiChip报告,台积电采用N3和N5制程的SRAM大小为0.0199μm2和0.021μm2,仅缩小了约5%。而N3E制程基本维持在0.021μm2,相较N5制程几乎没有微缩表现。

当前,CPU、GPU?和?SoC?在处理数据时将?SRAM用于各种缓存,并且从内存中获取数据的效率极低,尤其是对于各种人工智能(AI)和机器学习(ML)工作负载。但如今,即使是智能手机的通用处理器、图形芯片和应用处理器也携带着巨大的缓存。

未来,对缓存SRAM的需求只会增加,但对于N3(设置为仅用于少数产品)和N3E,这就无法减少SRAM占用的芯片面积,也无法降低与N5相比的新节点的更高成本。从本质上讲,这意味着高性能处理器的芯片尺寸将会增加,因此它们的成本也会增加。同时,与逻辑单元一样,SRAM单元也容易出现缺陷。

据悉,台积电计划推出其密度优化的N3S工艺技术,与N5相比,该技术有望缩小SRAM位单元的尺寸,但这将在2024年左右才能实现。

目前,SRAM缩微的方法主要有:一是采用多芯片设计,并将较大的缓存分解到更便宜的节点上的独立芯片中;二是使用替代内存技术,如eDRAM或FeRAM作为缓存,尽管后者有自己的特点。

本文内容参考财联社、半导体产业纵横综合报道

责编:Jimmy.zhang