英特尔的异构混合架构与手机处理器大小核设计有何不同?

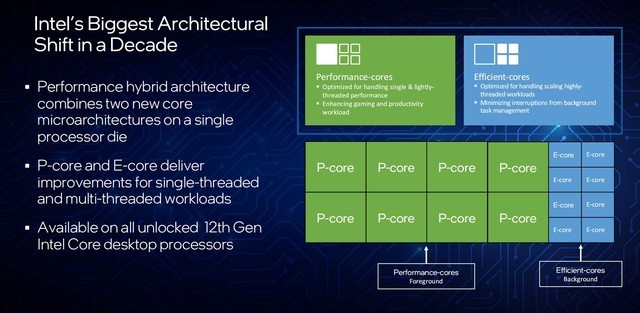

我们都知道,英特尔在12代酷睿处理器中采用了全新的架构设计,也就是异构混合架构。这一架构主要就是通过P-Core性能核+E-Core能效核设计,来弥补以往架构英特尔核心数量不足的短板。而这种设计也被大家习惯性地称为“大小核”。

在这种异构架构中,P-Core,即所谓的大核主要通过高频率与超线程负责重负载任务;而E-Core,即所谓的小核则主要负责较轻负载任务,以及多线程性能吞吐与协同能力。

同时,P-Core与E-Core采用了不同的微架构设计,前者为全新的Golden Cove微架构,后者为Gracemont微架构。

我们都知道,在ARM架构下,异构设计早已有之。而因为ARM架构下的异构设计中,一个核心主要负责性能,另一个核心主要负责低能耗,因此被用户形象的称为大小核设计。由于ARM架构主要面向移动级平台,如智能手机、平板电脑等,因此其大小核相对而言更加偏向能耗这一部分,毕竟对于这些移动级设备来说,低能耗、长续航、低热量是首先需要解决的问题。

但是对于PC而言,尤其是游戏本或桌面级PC来说,本身其实并不存在功耗和散热方面的担忧,因此英特尔P-Core+-E-Core混合架构设计,严格意义上来说并不等同于ARM架构的大小核。

其实就“大小核”来说,首先要清楚的一点是,在一个大小核异构架构下,大核是相对于小核而大的,小核是相对于大核而小的,如果跨越系统平台去单纯说小核一定就小,大核一定就大,无疑是不够严谨的。

那么英特尔的“大小核”与ARM的大小核究竟有何不同呢?

首先明确的一点是,12代酷睿Alder Lake的E-Core并不是单纯意义上的小核心。因为在英特尔异构架构体系下,Gracemont微架构的E-Core承担的是协同性的多线程吞吐性能提升,其实际性能超过了Skylake和Zen 2,而Skylake和Zen 2绝对不是小核心,它只是相对于Golden Cove的P-Core而言,能耗低一些。

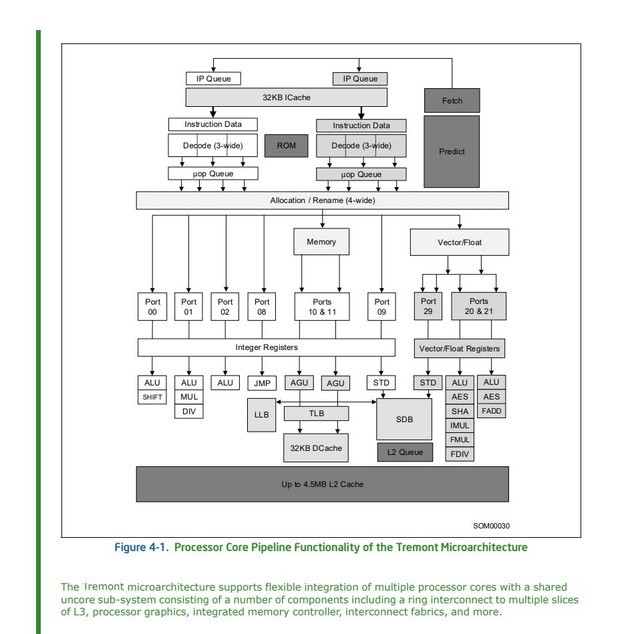

其次从命名来看,Gracemont无疑是源自Atom这一脉,其上一代微架构为Tremont,相对于Golden Cove微架构的P-Core而言,Gracemont微架构的E-Core确实要小一些,但其实际性能相对于Tremont来说,IPC提升超过20%。

其实对于12代酷睿来说,E-Core更重要的意义在于负责多线程任务的处理,如渲染、压缩/解压缩等等。而在Tremont上改进后的Gracemont,其实在渲染方面有着非常出色的性能表现。这源于其双前端六解码、以及整数浮点分离的设计。要知道,这种设计在ARM架构的小核中是没有的。

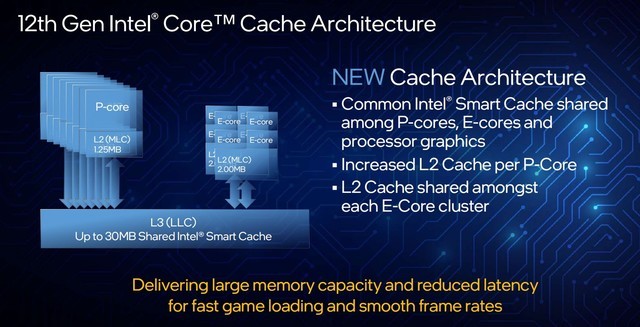

此外英特尔在混合架构之下对缓存进行了扩容,在增加了P-Core的二级缓存和E-Core的每核二级缓存的情况下,英特尔同时在共享L3智能缓存上也进行了增强和扩容。根据不同的核心数,英特尔12代酷睿处理器L3智能缓存最高提高到30MB,有效提高内存数据量、降低延时。

而在频率方面,E-Core睿频能力从3.6GHz起步到3.9GHz,表现也是相当不错了。

其实对于大小核设计,大家很容易被误导的一个地方是,“大小核”三个字就是简单描述核心的大小。其实从本质上来讲,这种描述忽略了大与小的参照系。在一个拥有大核心和小核心的异构架构中,大小核的界定除了考虑到核心面积之外,其实还要考虑到其发挥的作用。ARM架构下的小核心存在的主要任务就是负责低能耗,而12代酷睿中的“小核心”可并不是单单负责低能耗,它还要承担起更重负载的多线程任务,因此12代酷睿的“大小核”与ARM架构的大小核,其本质有着明显差异。