EUV光刻机最新路线图

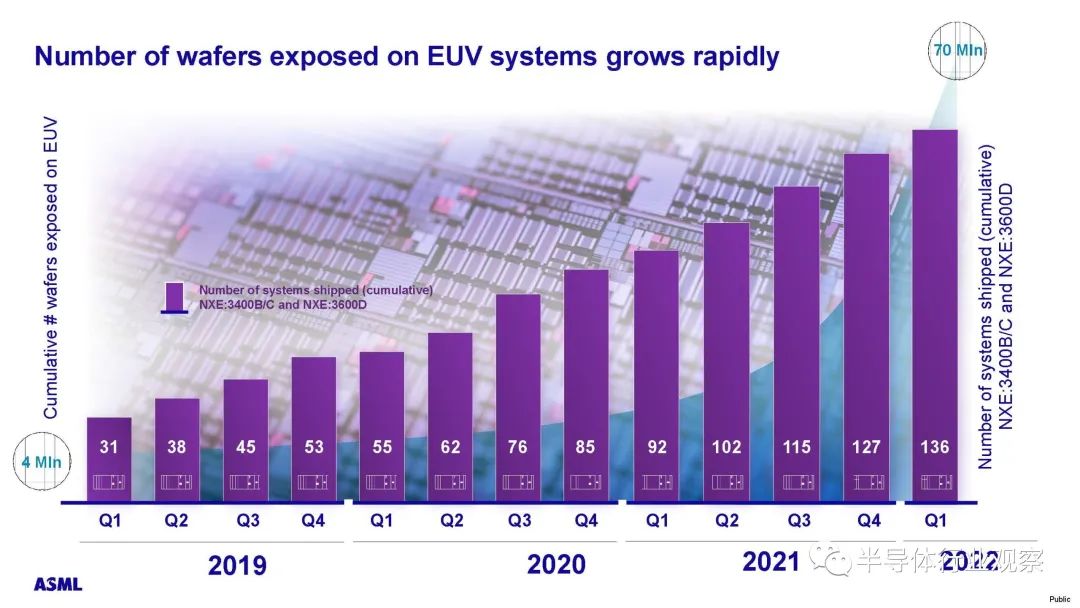

据semiwiki日前的报道,截至 2022 年第一季度,ASML 已出货 136 个 EUV 系统,约曝光7000 万个晶圆已曝光(如下图)。台积电在早前的技术大会上则表示,在全球已经安装的EUV光刻机系统中,台积电拥有了其中的 55%。三星的实际控制人李在镕日前则拜访了荷兰总统,以寻找更多的EUV供应。

这再次说明,生产先进芯片必不可少的EUV成为了全球关注的目标。在日前的一些报道中,我们也看到了EUV光刻机的一些路线图更新。

0.33NA EUV的新进展

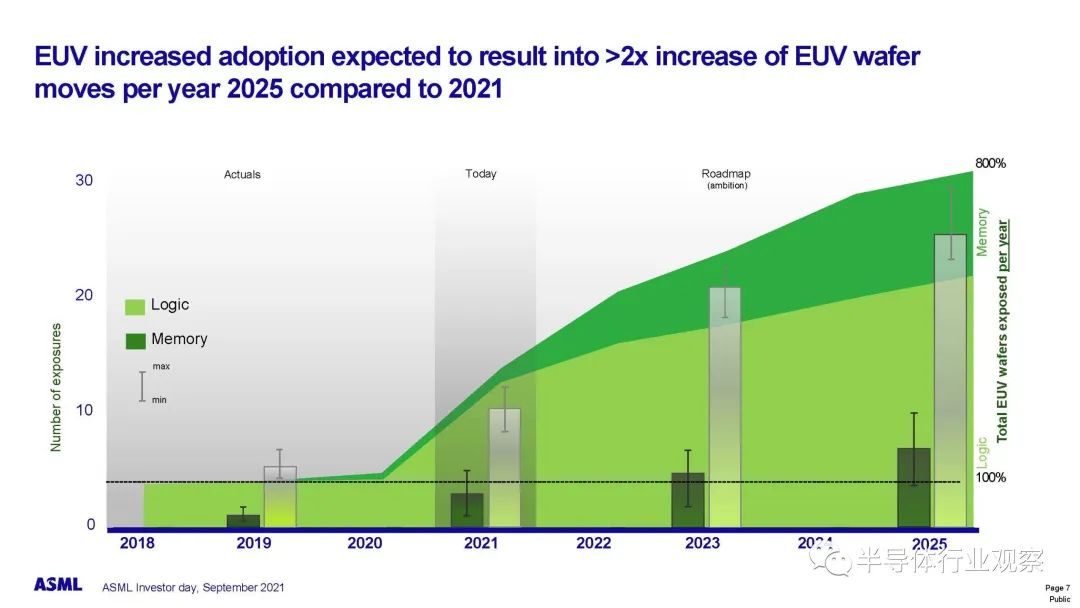

报道中表示, 0.33 NA的 EUV 系统是当今前沿光刻的主力生产系统。先进的逻辑和 DRAM都在使用0.33 NA 的系统大批量生产。下图说明了逻辑和 DRAM(条)的EUV层数和每年使用EUV曝光的晶圆(面积)。

据ASML公司的Mike Lercel介绍 ,以典型的5nm工艺为例,2021 年的逻辑值是 10 层以上 EUV 层,到2023 年的3nm将会有20层的EUV层,而DRAM 目前的EUV层使用量约为 5 层。Mike Lercel还谈到了未来 DRAM 曝光的展望,他指出,不就之后DRAM上有大约会有 8 个关键层,最终其中一些层可能需要多重图案化,使每个晶圆的 EUV 曝光达到 10 层。

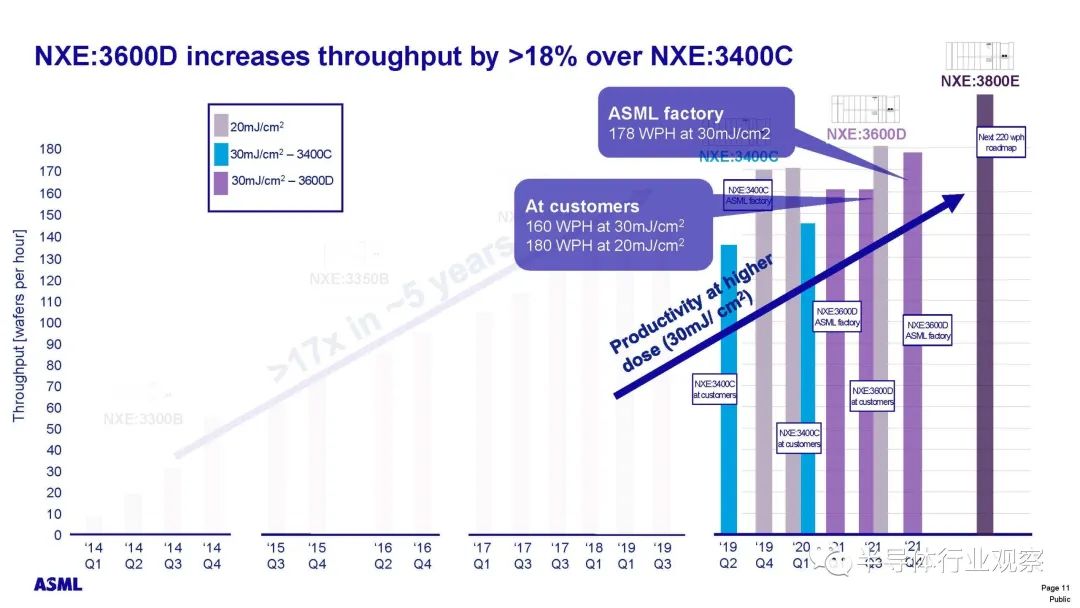

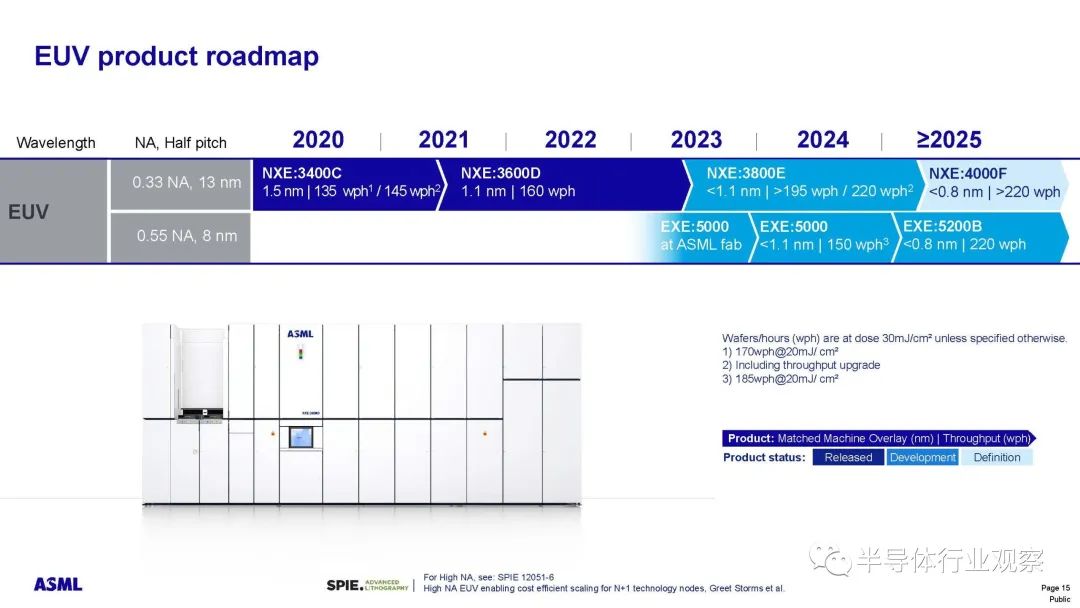

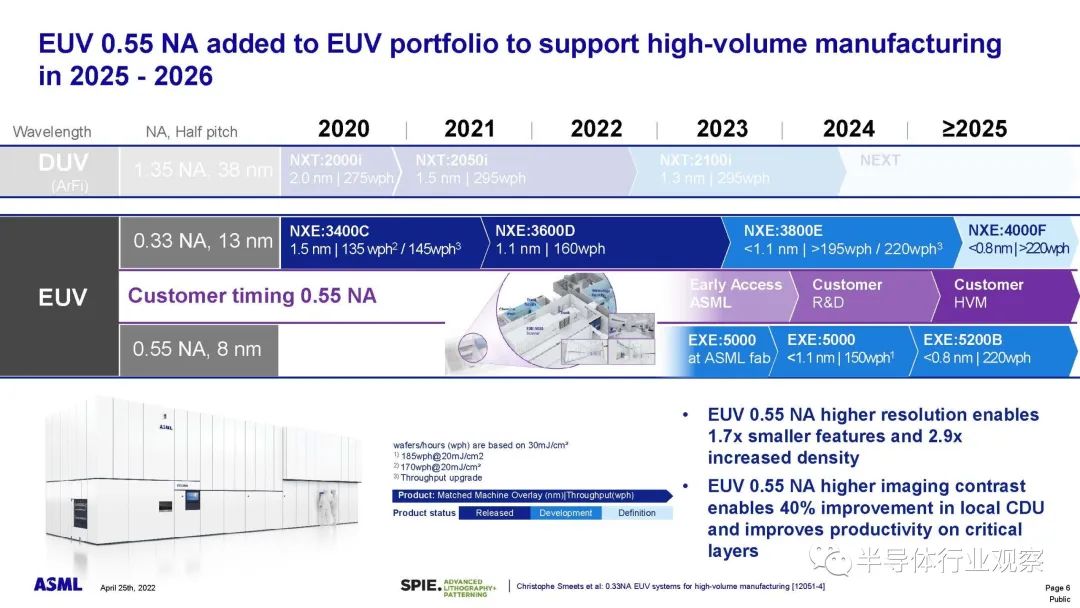

从报道中可以看到,新型号的EUV光刻机系统 NXE:3600D将能达到93%的可用性,这将让其进一步接近DUV光刻机(95%的可用性)。数据显示,NXE:3600D 系统每小时可生产 160 个晶圆 (wph),速度为 30mJ/cm2,这比 NXE:3400C 高 18%。二正在开发的 NXE:3800E系统最初将以 30mJ/cm2的速度提供大过195wph的产能,并在吞吐量升级后达到220wph。据介绍,NXE:3600E 将在像差、重叠和吞吐量方面进行渐进式光学改进。

从semiwi的报道中我们可以看到,在0.33 NA的EUV光刻机领域,ASML 路线图包括到 2025 年左右推出吞吐量约为220wph 的 NXE:4000F。按照EUV 执行副总裁Christophe Fouquet在参加高盛虚拟峰会的时候的说法,公司之所以把新设备称它为 F,因为ASML也希望通过该设备能显著提高生产力,这主要归功于公司希望在该系统的功率上能够更进一步。至于产能的增加幅度,Christophe Fouquet表示,这可能会达到10%到20%,但他们依然还没有最终确定。不过ASML目前计划在 2025 年左右交付第一个NXE:4000F系统。

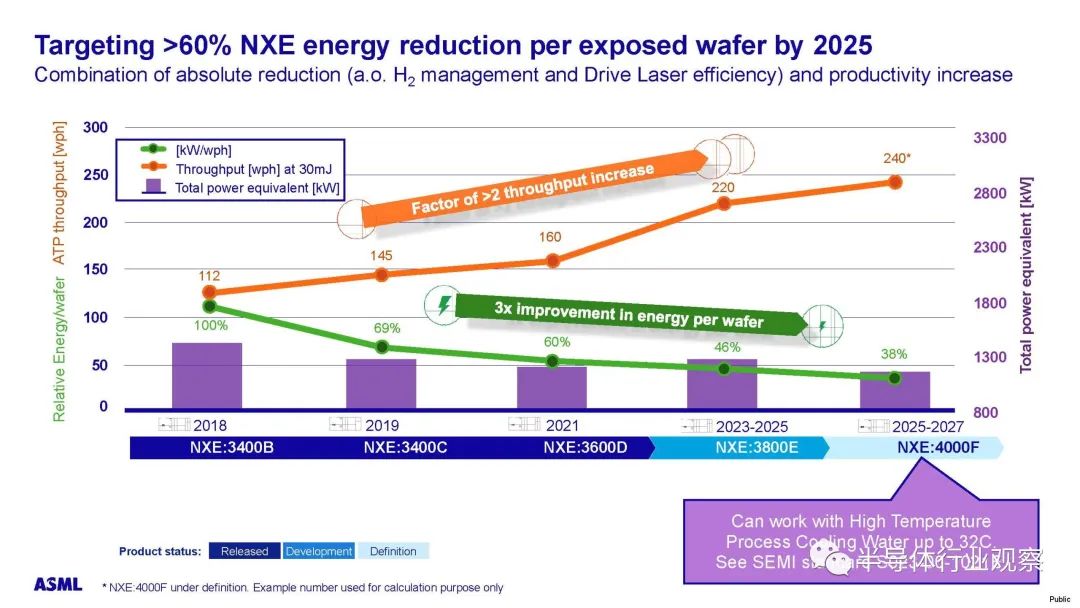

semiwiki在文章中表示,对于 0.33 NA 系统,ASML 正致力于通过增加吞吐量和降低总能量来减少每次曝光所需的功耗,而双重图案甚至也将成为0.33NA光刻机需要发力的一个方面。

如在之前的报道中指出,在发力0.33 NA光刻机的时候,ASML也在加快0.55 NA光刻机的进度。而继英特尔表示将在2025年使用上High-NA光刻机之后,台积电在日前也将High-NA光刻机的应用时间放在2024年。这无疑是大大提升了先进EUV光刻机的应用时间。

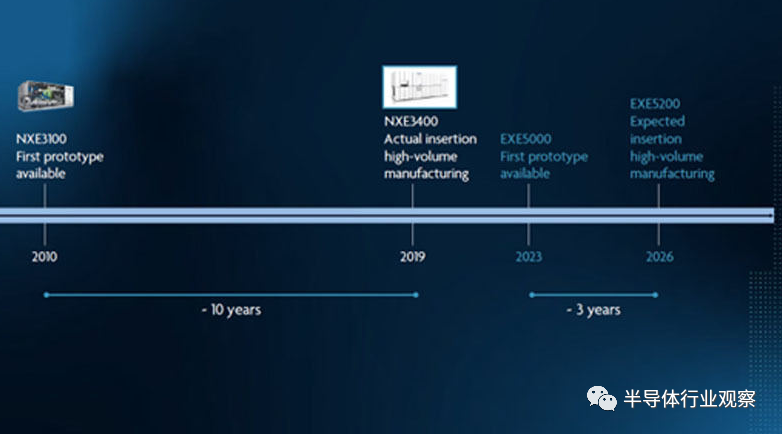

因为从相关资料可以看到, 0.33 NA的常规 EUV 光刻机从原型机出货(2010 年)到量产机出货(2019 年)用了大约10 年时间。如果相关报道属实,那就意味着 0.55 NA 的high NA EUV 光刻机从原型机出货(2023年)到量产机出货(2026 年)只需要短短的三年。

0.55 NA EUV光刻机的目标

关于为什么要提升EUV光刻机的NA,这在很多文章中也都谈过。

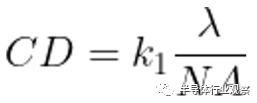

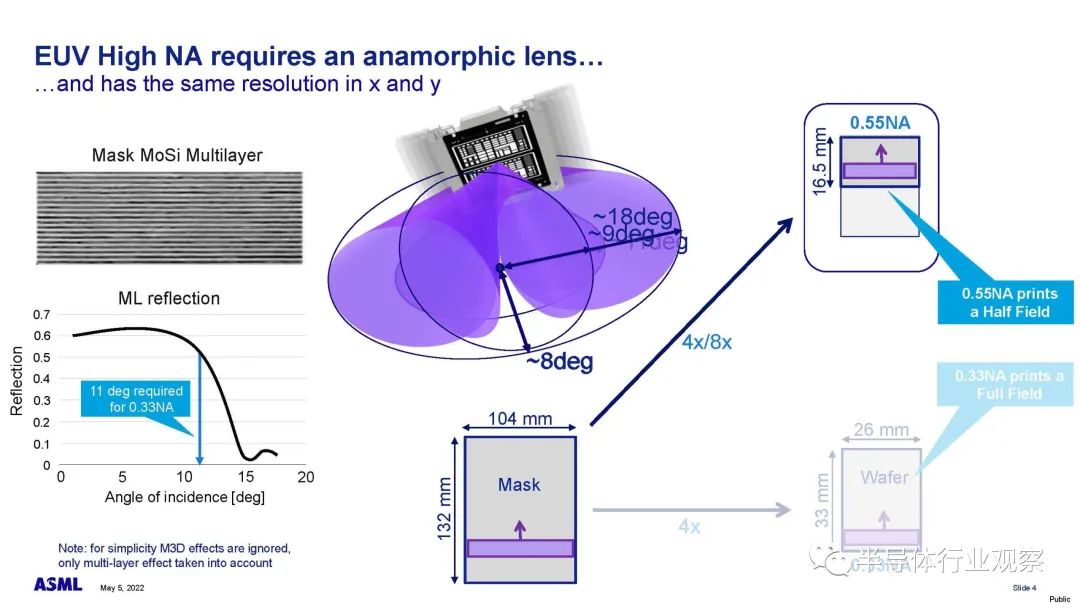

归根到底,高数值孔径 EUV 系统的好处可以用一个词来概括——分辨率。因为根据瑞利公式,将孔径从0.33增加到 0.55,可以成比例地提高可实现的临界尺寸——从0.33 NA 系统的 13nm提升到0.55 NA EUV 可能低至 8nm。

在上个月举办的 SPIE 会议上,ASML 和蔡司报告说,虽然开发正在按计划进行,但预计要到 2023 年才能安装第一个0.55 NA EUV系统。如图所示,ASML 的路线图将第一个High NA 系统 (EXE:5000) 安装在 ASML 工厂的实验室中,并于 2023 年与 Imec 联合运行,以进行初步评估。EXE:5000 系统应在 2024 年交付给客户,生产型 EXE:5200 系统应在 2025 年左右交付给客户用于生产使用,

在semiwiki的文章里他们谈到,High-NA 的光学器件比 0.33 NA 的要大得多,需要独特的设计方法。0.55 NA 系统将具有一个变形镜头系统,在一个方向上具有 4 倍的缩小率(与 0.33 NA 相同),在正交方向上具有 8 倍的缩小率。由于reticle的尺寸和 8 倍的缩小,可打印区域尺寸在扫描方向上减半至 16.5nm。

为了更快地推动High NA EUV光刻机落地,ASML正在和很多研究机构和企业携手,如imec就是他们一个很重要的合作火棒。

imec执行长Luc Van den hove表示,imec与ASML合作开发High-NA技术,ASML现在正在发展首台0.55 High-NA EUV微影扫描设备EXE:5000系统的原型机。他指出,与现有的EUV系统相比,High-NA EUV微影设备预计将能在减少曝光显影次数的情况下,实现2奈米以下逻辑芯片的关键特征图案化。

而为了建立首台High-NA EUV原型系统,imec持续提升当前0.33 NA EUV微影技术的投影解析度,借此预测光刻胶涂布薄化后的成像表现,以实现微缩化线宽、导线间距与接点的精密图案转移。同时,imec携手材料供应商一同展示新兴光刻胶与涂底材料的测试结果,在High-NA制程中成功达到优异的成像品质。同时也提出新制程专用的显影与蚀刻解决方案,以减少微影图案的缺陷与随机损坏。

从这个描述中我们可以看到,对于0.55 NA的光刻机,需要更新的不但是其光刻机系统。同时还需要在光掩模、光刻胶叠层和图案转移工艺等方面齐头并进,才能让新设备应用成为可能。

生态系统全力以赴

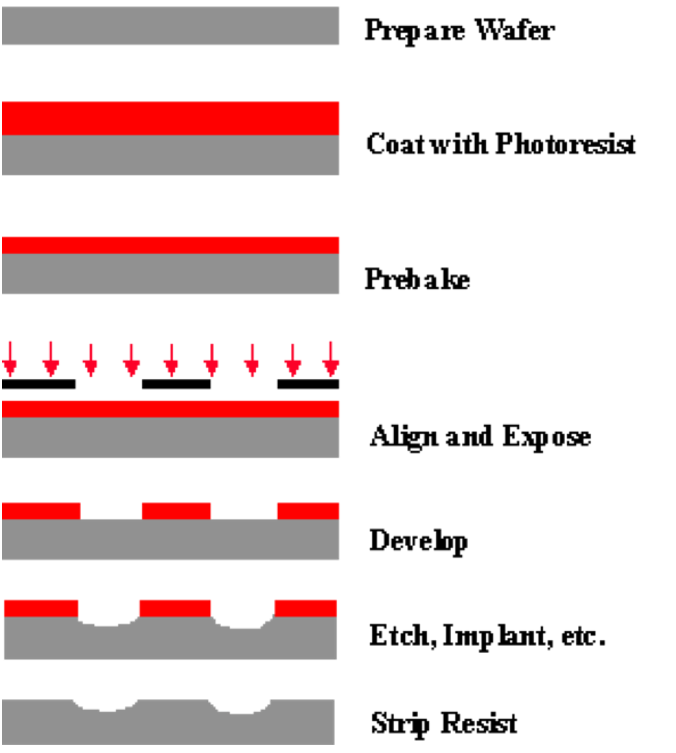

在晶圆厂中,芯片制造商需要利用光刻机和其他设备来生产芯片。使用在设计阶段生成的文件格式,光掩模设施创建掩模。掩模是给定芯片设计的主模板,最终被运送到晶圆厂。从那里,晶圆被插入到涂层机/显影系统中。该系统将一种称为光刻胶的光敏材料倒在晶圆上。

然后,将掩模和鬼片插入光刻扫描仪中。在操作中,扫描仪产生光,光通过一组投影光学器件和系统中的掩模传输。光照射光刻胶,在硅片上形成图案。

从过往从DUV到EUV升级一样,来到High-NA EUV上也需要新的光掩模类型。因为在更高的孔径下,光子以更浅的角度撞击掩模,相对于图案尺寸投射更长的阴影。“黑暗”、完全被遮挡的区域和“明亮”、完全曝光的区域之间的边界变为灰色,从而降低了图像对比度。

据Semiengineering报道,有几个选项可用于降低有效吸收器(effective absorber)高度,从而降低 3D 掩模效果的影响。第一个也是最简单的方法是减小吸收材料的厚度。

Imec 高级图案化项目总监 Kurt Ronse 在接受Semiengineering时表示,由High NA EUV 图案化的第一层可能具有相对宽松的尺寸,约为 28nm。简单地降低吸收器高度应该提供足够的对比度。然而,随着功能不断缩小,制造商将需要重新考虑吸收材料。Erdmann 指出,目前使用的钽基吸收体(tantalum-based absorber)的光学特性相对较差。降低吸收体的折射率将改善剂量-尺寸特性,在恒定曝光剂量下实现更小的特征。同时,增加消光系数会减少三维效应。

然而,n和k不是掩模制造商可以简单地在工艺刻度盘上设置的独立参数,它们是材料属性,因此彼此相关,并与吸收器的其他特性相关。为了采用新材料,掩模制造商必须能够蚀刻它并修复缺陷。目前用于钽吸收体的反应性离子蚀刻是一些候选材料的一种选择,但新的吸收体仍可能需要新的蚀刻工艺和新的化学物质。“因为接触层和金属层有不同的要求,他们可能也需要不同的吸收体。:Ronse 说。

按照他所说,在这方面还没有出现共识选择,然而为了继续进行工艺开发,掩模制造商也需要行业的额外指导。

Semiengineering进一步指出,光在穿过光掩模的吸收器图案后,EUV 光子遇到硅片及其光刻胶层( photoresist blanket)。减小的焦深使得同时保持光刻胶叠层的顶部和硅片平面聚焦变得更加困难。如果焦点错误使相邻特征靠得太近,则间隙无法清除并出现桥接缺陷。如果特征之间的空间太大,则所得到的光刻胶特征太薄并在其自身重量下塌陷。

因此降低光刻胶的厚度既可以提高焦点,又可以降低图案崩塌的风险。但与此同时,也会带来额外的挑战。如在报道中披露,一种有希望的替代品是金属氧化物光刻胶。

据报道,这种光刻胶使用入射光子来分解氧化锡纳米团簇( tin-oxide nanoclusters)。氧化物簇(oxide clusters )可溶于显影剂中,而金属锡则不溶于。这些是负性光刻胶。曝光使材料不溶。金属氧化物本质上更耐蚀刻并吸收更多的 EUV 光子,从而使它们能够以更薄的层实现可比的结果。但不幸的是,接触孔,可能是高数值孔径 EUV 曝光的第一个应用,然而它需要正的光刻胶。

此外,其他与 EUV 相关技术也在研究中,例如 pellicles。这是一个用于覆盖掩膜,防止颗粒落在其上的产品。

相关报道指出,ASML 开发了新的 EUV pellicles。同时,Imec 的碳纳米管pellicles在 ASML 的 EUV 扫描仪上的透射率达到了 97.7%。单壁和多壁pellicles都是有前途的。按照Imec 技术人员的主要成员 Emily Gallagher 所说:“这两种类型都表现良好,在 CD 均匀性、LWR 和耀斑方面,与无pellicle参考相比,成像差异极小。根据测量的这些pellicle的 EUV 吸收率在 95.3% 到 97.7% 之间,预计剂量会略有增加。”

写在最后

在生态系统的共同努力下,ASML正在努力土推动High-NA光刻机成为可能。与此同时,他们还在加大EUV光刻机的产能提升,并与产业一起,推动这些先进的技术面向更多的应用。

根据ASML 在一季度财务会议上披露的数据,公司的目标是在 2022 年出货 55 台 EUV系统,并到 2025 年实现(最多)90 台工具的计划。ASML 同时还承认, 90 台可能超过 2025 年的实际需求,不过他们将其描述为为满足2030 年 1 万亿美元半导体行业需求所做出的巨大努力。

Christophe Fouquet在高盛的会议上则强调,High NA EUV光刻机将首先在逻辑芯片上应用,随后,DRAM乃至3D DRAM也会是High NA EUV光刻机关注的方向。同时,他最后还说道:“在可预见的未,EUV 不会很快进入中国,因为美国政府目前的立场是相当强硬。”