三星与台积电的决战时刻

不过,眼下的他已无暇顾及,根据《韩国先驱报》的爆料,李在镕的旅欧首站将定在荷兰的埃因霍温,这里正是光刻机巨头ASML的总部所在地。

就在李在镕动身启程的一个月前,三星对旗下晶圆代工厂发起了一轮内部审核,调查用于提升良率的资金是否有所落实,因为目前试生产的3nm芯片良率已经低到“让高层难以置信”。审核的结果是三星DS(半导体事业暨装置解决方案)部门半数高层被清洗,原三星电子副总裁兼闪存业务总经理宋子赫接任DS总经理一职。

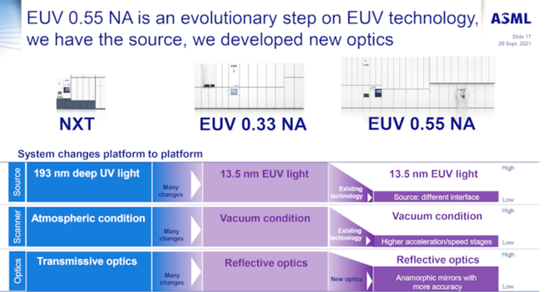

毫无疑问的是,李在镕此行是为了抢夺ASML光刻机的优先供货权,以保证晶圆代工业务的顺利进行。从ASML的供货时间表来看,这家公司今年将向三星交付18台EUV极紫外光刻机,这其中就包括目前三星最关心的Twinscan EXE:5000 系列——具有 0.55 NA(高 NA)镜头,能够实现 8nm 分辨率,完全可以满足3nm芯片的生产需求。

图片来源:ASML官方网站

按照计划,三星将在今年第三季度量产3nm制程芯片,但就目前的良率及设备交付情况来看,这个目标似乎难以实现。

几家欢喜几家愁。就在三星为3nm芯片上市一筹莫展时,6月10日,海通国际的分析师Jeff Pu在报告中做出预测,台积电将在今年下半年向苹果批量交付3nm制程的M2 Pro芯片,足以说明眼下台积电的3nm工艺已经具备量产条件。

这或许是三星最不愿意看到的一幕,在痛失高通的8+Gen1订单后,3nm先进制程芯片的这场战争,他们没有退路。

输不起的3纳米

可能是受到三星DS部门良率造假的影响,5月24日,三星电子宣布未来5年将投资3600亿美元用于半导体和生物制药等行业,其中80%将用于研发和人才培养,尤其是在先进逻辑芯片领域。

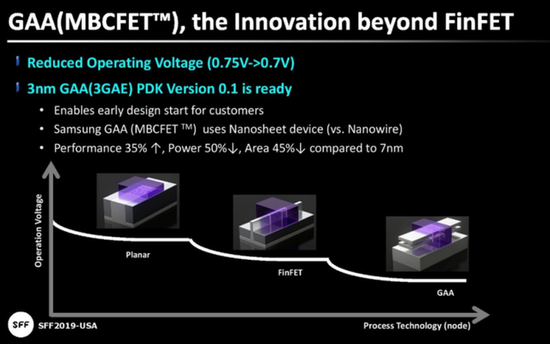

除了大幅提高的资金投入外,三星几乎是以一种“毕其功于一役”的姿态去发展3nm制程芯片,十分激进地改用GAA(环绕式栅极)工艺,相比于过于行业内早已轻车熟路的FinFET(鳍式场效应晶体管)工艺,前者在业内还未有成功开发的先例。

三星的这次技术整改颇有几分“推倒重建”的意味。

需要说明的是,尽管三星在先进逻辑芯片的制程上与台积电亦步亦趋,但在性能上三星可能要落后前者半代甚至更多。以晶体管的密度为例,三星4nm工艺的密度是145.8MTr/mm,尚不如台积电5nm的171.3MTr/mm。

那么三星有没有反超的时机呢?实际上,当下这场从FinFET到GAA的工艺变革就是三星最佳的机会。

图片来源:SFF,三星晶圆代工论坛

引起这场革命的是CMOS器件天生存在的“短沟道效应”。我们常说的14nm、7nm工艺节点实际指的是晶体管导电沟道的长度(由于沟道长度不容易被观测,业界通常用更加直观且接近的栅极长度代指工艺节点)。在10nm工艺出现之前,沟道长度就是指芯片工艺,虽然目前各种工艺节点已基本等于数字营销的游戏。

不过,沟道长度依然是一个重要的指标,因为CMOS器件功能越复杂,晶体管的密度就会越大,这就必然需要沟道长度越来越小。可问题是,随着沟道长度的缩短,沟道管中的源级和漏极的距离也会越来越短,因此栅极很难再保证对沟道的控制能力,也意味着栅极电压夹断沟道的难度变大,即产生短沟道效应,从而出现严重的电流泄露。

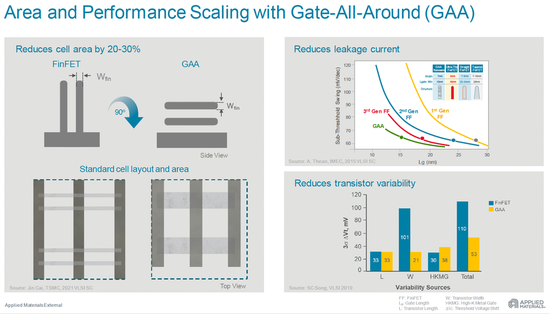

如今5nm和4nm制程存在的发热和高能耗问题,本质上就是短沟道效应的显现,这个问题也与业内普遍使用的FinFET工艺有关,由于FinFET采用的三面栅结构缺失其中一个方向的栅极包裹,随着芯片制程的减少,FinFET的三面栅结构的漏电控制能力也相应的减弱。

因此,三星的想法就是,既然FinFET在3nm制程的芯片上已经出现了无法克服的设计问题,干脆就直接弃用这个结构,转用四面环绕式的GAA工艺。

图片来源:美国应用材料公司官方网站

虽然GAA取代FinFET已成业内共识,但现阶段影响其量产普及的因素还有不少,复杂的制造流程、良品率、成本难以控制等等仍是阻碍。

据《wccftech》的报道,三星的晶圆代工部门3nm制程的芯片良率目前只能维持在10%-20% 之间。相比之下,台积电4nm制程的良率已经可以达到70%,虽然这样的对比于三星而言并不公平,因为GAA作为一众全新的工艺其开发难度要远大于台积电同类产品。

但芯片设计厂商不会给三星慢慢改进的时间。比如此前《Business Korea》曾报道过目前三星4nm工艺的良率也不尽如人意,仅为30%-35%之间,如此低效的质量控制让高通在在骁龙8+ Gen1发布之前,紧急由三星转单交给台积电来代工生产。

因此三星在3nm这个工艺节点下,根本就不敢输,也不能输。

对于台积电而言,3nm制程芯片同样是关键一役,因为台积电仍然坚持使用更加成熟且传统的FinFET工艺,如何在3nm制程的节点下,打破物理意义的工艺上限,这是摆在台积电面前的一道难题。

6月10日,台积电宣布2nm晶圆代工厂的评审文件已提交送审,第一期工厂预计在2024年底前投产,这家公司此前曾披露过,整个2nm制程芯片的研发费用可能高达340亿美元,按照3nm今年下半年上市的时间节点来看,这一制程的芯片肩负着维持台积电未来两年庞大现金流和业绩增长的重任。

鹿死谁手?

在去年第四季度,三星电子的代工业务市场份额上升了1.1个百分点,达到18.3%,台积电的份额下滑1.0个百分点至52.1%。两家公司市场份额差距缩小2.1个百分点至33.8%。值得一提的是,在同一时期业内前五大芯片制造商中,三星是唯一一家市场份额增长的公司。

三星电子财报显示,去年第四季度,旗下代工业务销售额环比增长15.3%,三星在财报中将增长归功于“开始大规模生产主要客户高通公司新旗舰产品”。

这其实充分反映了目前IC设计行业内的现状,即行业资源被头部企业牢牢掌控,排在前列的高通、英伟达等公司在体量上的差距与其他公司越来越大,已经完全可以靠单一产品影响业内最大代工厂的业绩。

这种行业格局很难评价好坏,但对于代工厂而言,一旦失去芯片设计公司旗舰产品的代工订单,其影响可能在短时间内无法逆转,比如前不久三星痛失高通8+Gen 1的订单,这可能直接导致三星在今年无法维持此前高增长的态势。

根据TrendForce预测,2022年全球代工市场预计将增长20%,达到1287.84亿美元。其中台积电在全球代工市场的份额预计今年将增长到56%,而三星电子的份额可能从18%下降16%。

而在短时间内,三星也很难扭转自身的不利局面,尽管三星在台积电之前完成了3nm的流片,但从流片到量产三星还有许多问题亟待解决,比如前文中所提到的良率问题。

再有就是二者在产能上的差距。由于台积电具备动态调配生产线能力,其产能利用率甚至可以提高到110%-120%,这是三星完全无法企及的,更何况三星的逻辑芯片产能中约有一半自用,而台积电作为纯晶圆代工厂,集团内的其他业务根本不需要占据芯片产能。

当然,三星也并非毫无胜算,台积电FinFET工艺能否在3nm制程节点上适用?在第一款商用3nm芯片落地之前,没人能给出答案,但这也是三星最大的底气。

实际上,这场“代工双雄”之间的竞争没有谁会输的彻底,因为这个行业中的绝大部分厂商已经完全告别了先进制程的竞赛,比如过去耳熟能详的格罗方德和联华电子,眼下都只能靠着28nm制程产品线去维持市场,“摩尔定律”在这些公司身上已基本失效。

随着双寡头拉起的3nm制程竞赛,未来行业内的晶圆代工订单势必将向这两家公司进一步集中,由于半导体行业极度依赖规模效应,未来晶圆代工这个行业也很难再有新的挑战者出现。

写在最后

三星电子向来以“全产业链方案解决商”的形象自居,但从内部审查再到管理层换血,这些无时无刻展示着这个庞然大物的弊端:内部管理与部门协同之间的低效。

有人说三星移动部门、DS部门、LSI(芯片设计)部门所组成的并不是铁三角,而是“推诿三角”,三星手机抱怨LSI部门的方案落,LSI部门认为是DS部门的质量控制问题让他们无法做出好的产品,DS部门又反咬LSI部门在设计商存在缺陷……

这些问题好像并不会随着掌门人亲自抢购光刻机就能得到解决。巧合的是,同样是在6月,也同样是在欧洲,三星的创始人李健熙29年前于法兰克福发表了著名的“新经营宣言”,豪言“除了老婆孩子不能变,其他一切都会变”。

这句话对于今天的三星电子大概同样适用。