重磅!0.2nm路线图来了!详细讲解技术实现!

世界上最先进的半导体研究机构?Imec?最近在比利时安特卫普举行的未来峰会上分享了其亚1nm和晶体管路线图。

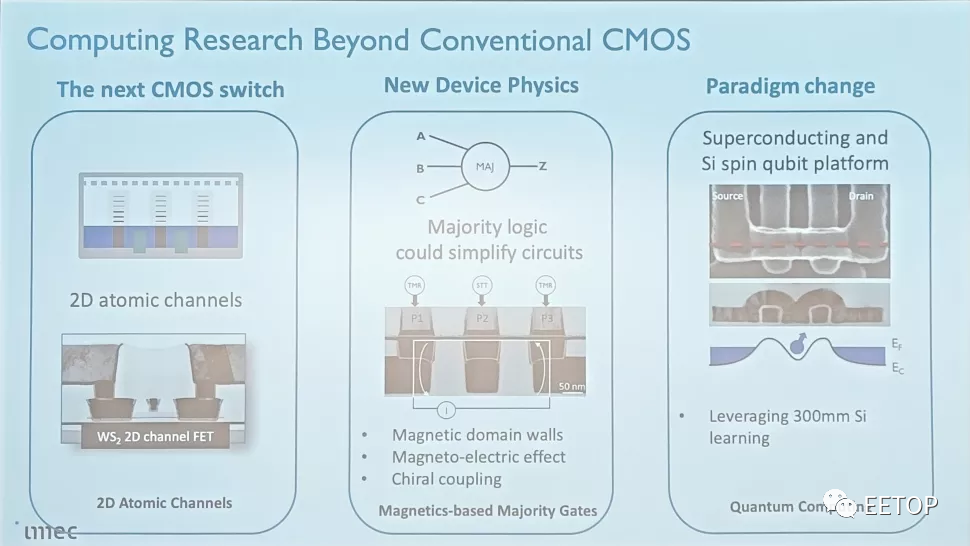

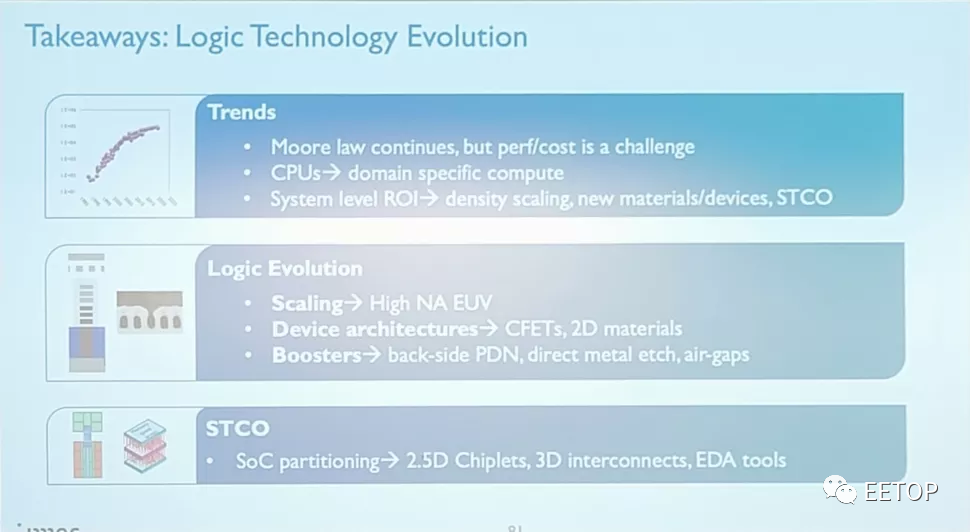

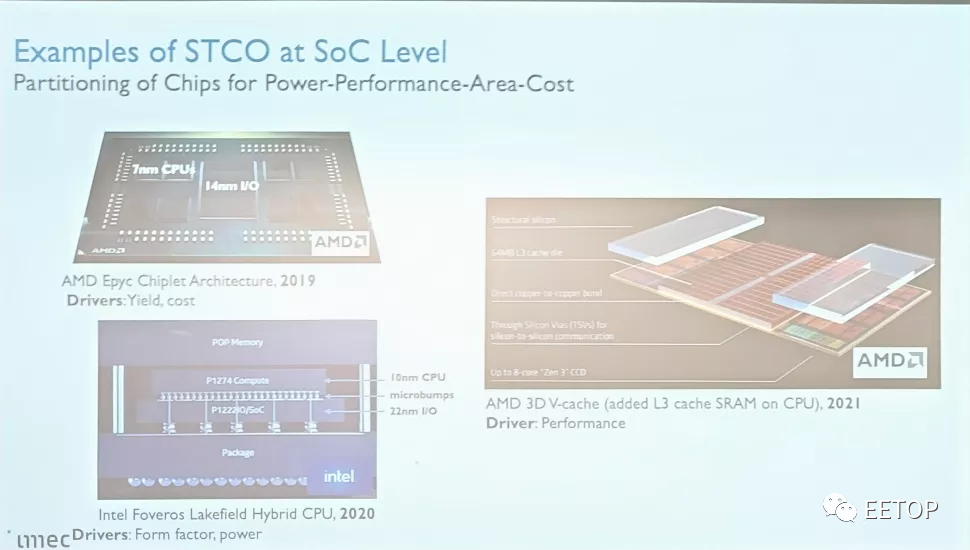

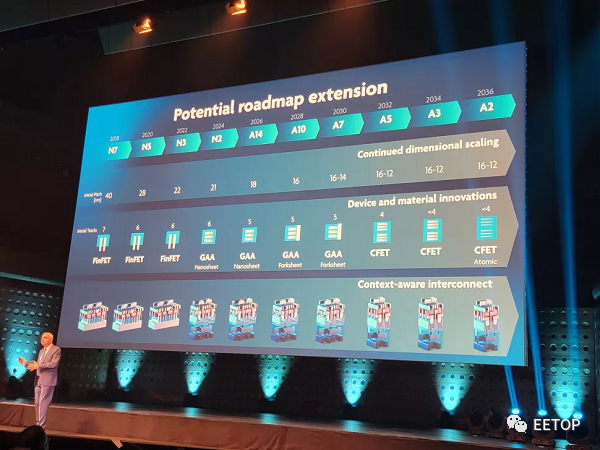

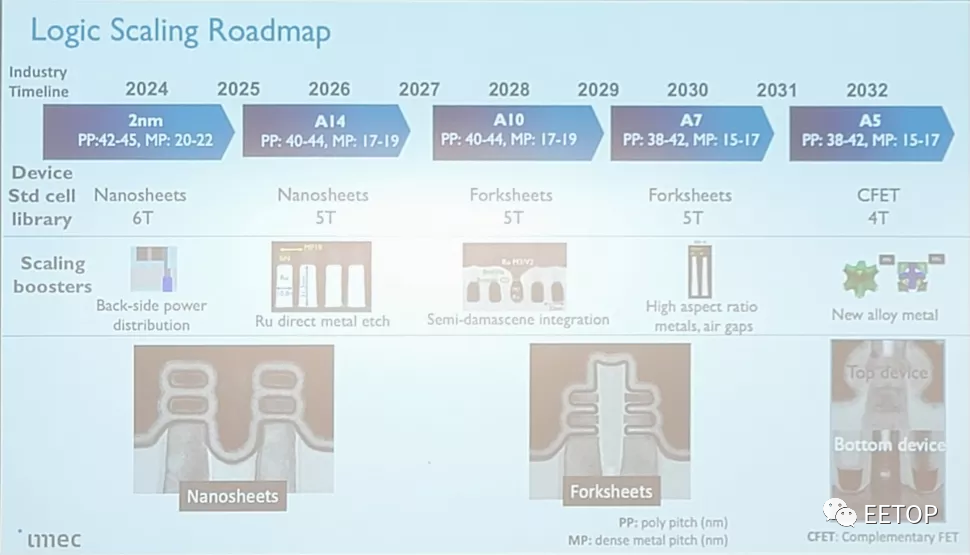

该路线图让我们大致了解了到 2036 年Imec将在其实验室与台积电、英特尔、三星和 ASML 等行业巨头合作研发的下一个主要工艺节点和晶体管架构的时间表。该路线图包括突破性晶体管设计,从持续到 3nm 的标准 FinFET 晶体管发展到新的 Gate AllAround (GAA) 纳米片和叉片设计,分别为 2nm 和 A7(7 埃),然后是突破性设计,如 CFET 和原子A5 和 A2 的通道。提醒一下,十埃等于 1nm,因此 Imec 的路线图包含亚1nm工艺节点。

定义问题

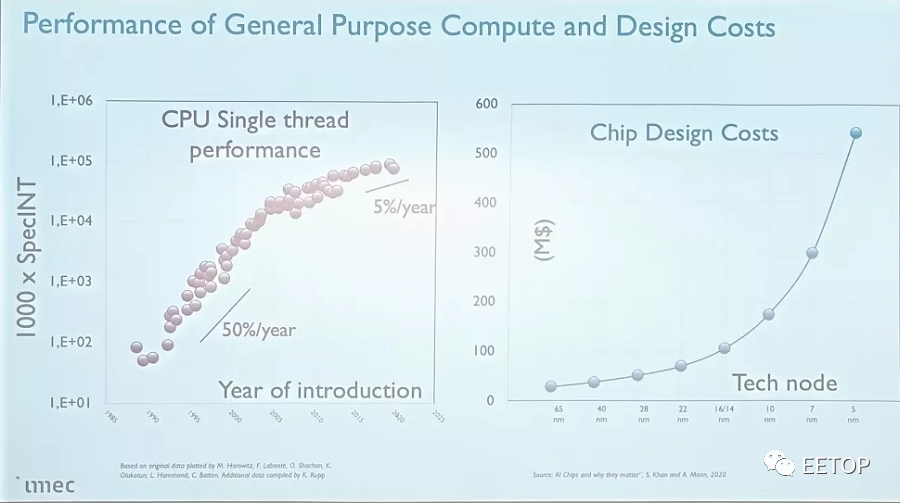

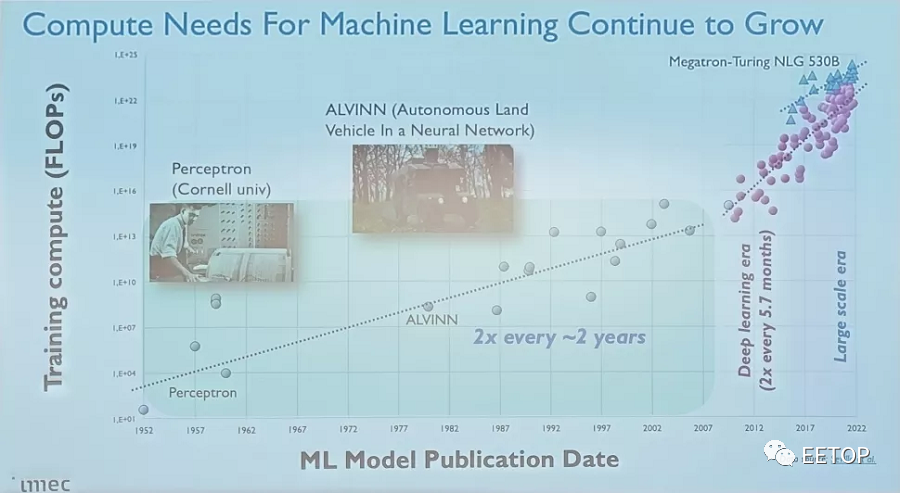

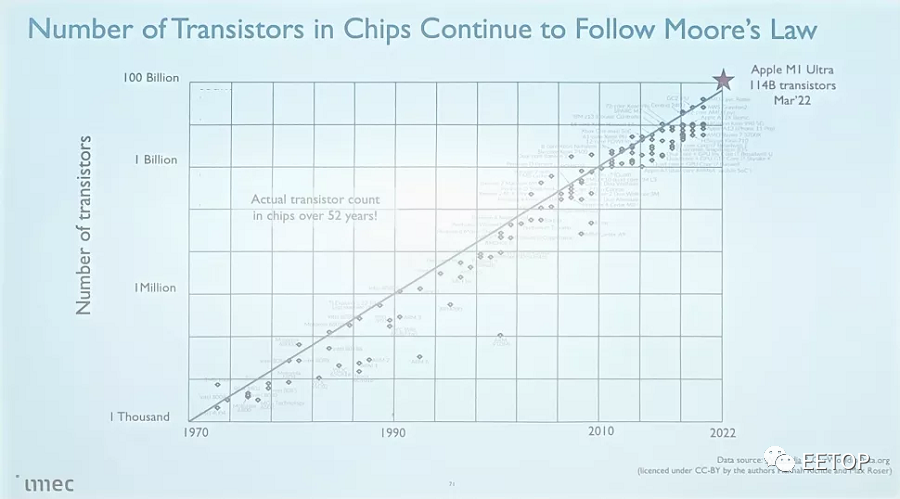

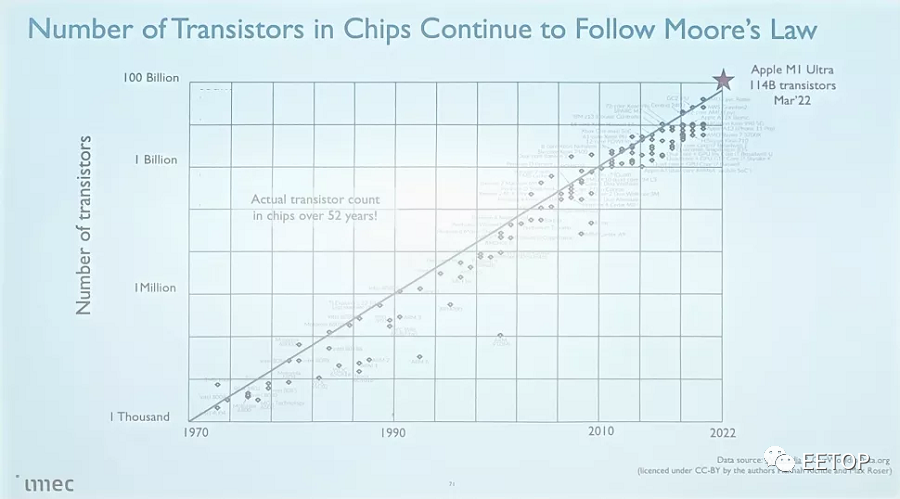

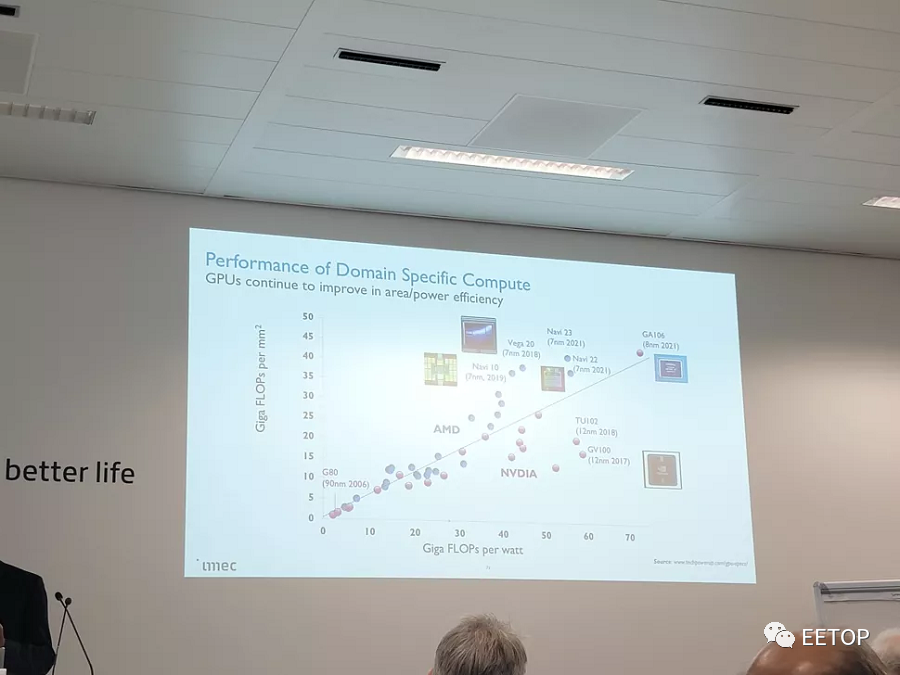

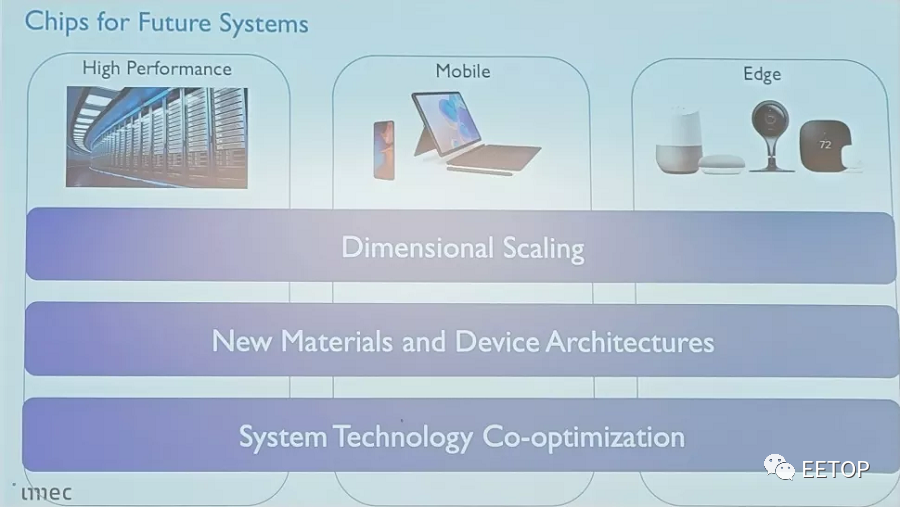

随着节点的进步、成本的飙升以及对更多计算能力的需求,尤其是机器学习的非线性增长,该行业面临着越来越多的挑战。

Imec 的晶体管和亚 1nm 工艺节点路线图

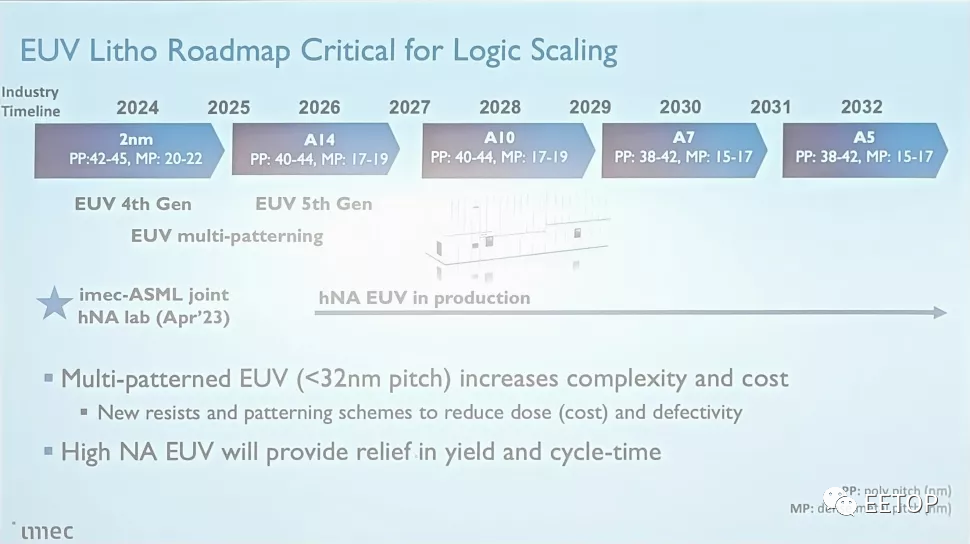

第一步是启用下一代设备。今天的第 4 代 EUV 光刻机的孔径为 0.33,因此芯片制造商将不得不使用多重图案技术(每层超过一次曝光)来创建 2nm 及以上的最小特征。由于晶圆必须为单层“印刷”两次,因此出现缺陷的可能性更高。这将导致产量降低和周期(生产)时间延长,从而导致成本增加。下一代 High-NA 型号(第 5 代)的孔径为 0.55。这种更高的精度将允许在单次曝光中创建更小的结构,从而降低设计复杂性并提高产量、周期时间(每小时 200 多片晶圆)和成本。Imec 和 ASML 预计这些工具将在 2026 年用于量产。第一个价值 4 亿美元的高 NA 工具将于 2023 年上半年在 ASML 完成。Imec 将在 ASML 设施的测试实验室运行,以加快芯片制造商对机器的访问速度(ASML 通常将该设备运送到 imec 的晶圆厂)。

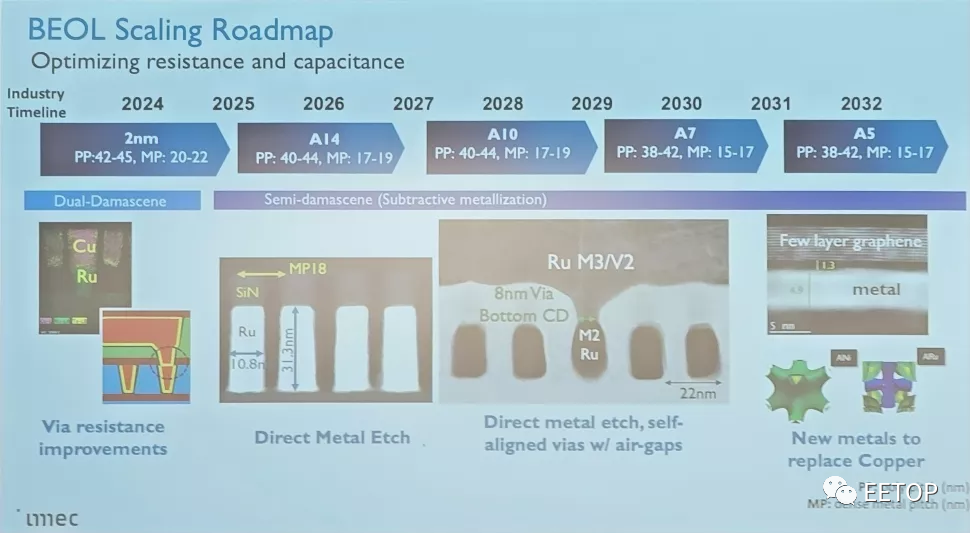

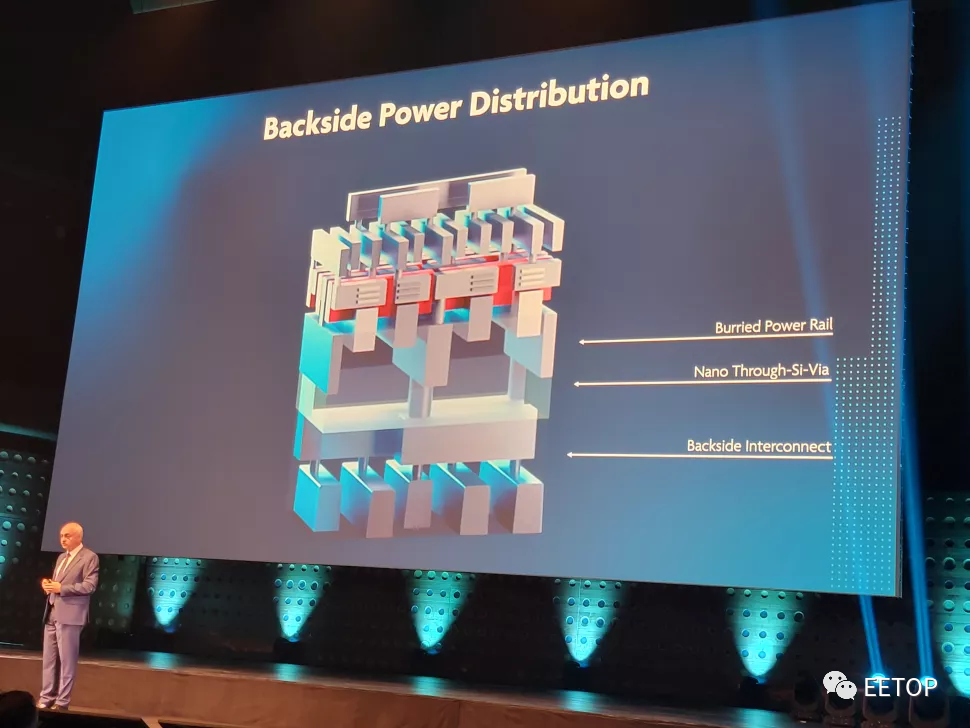

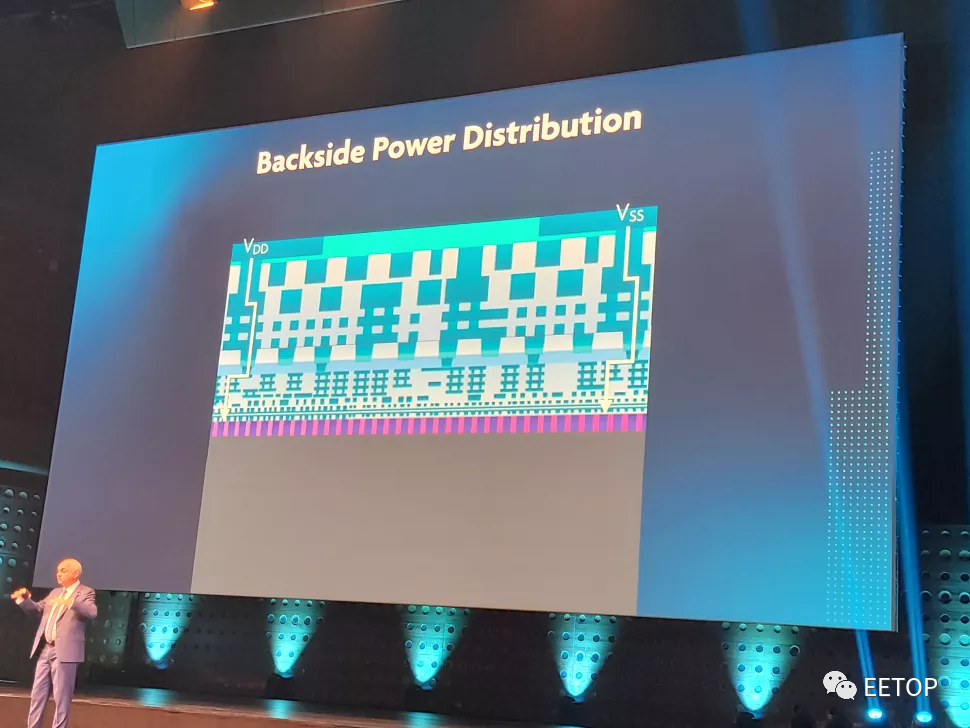

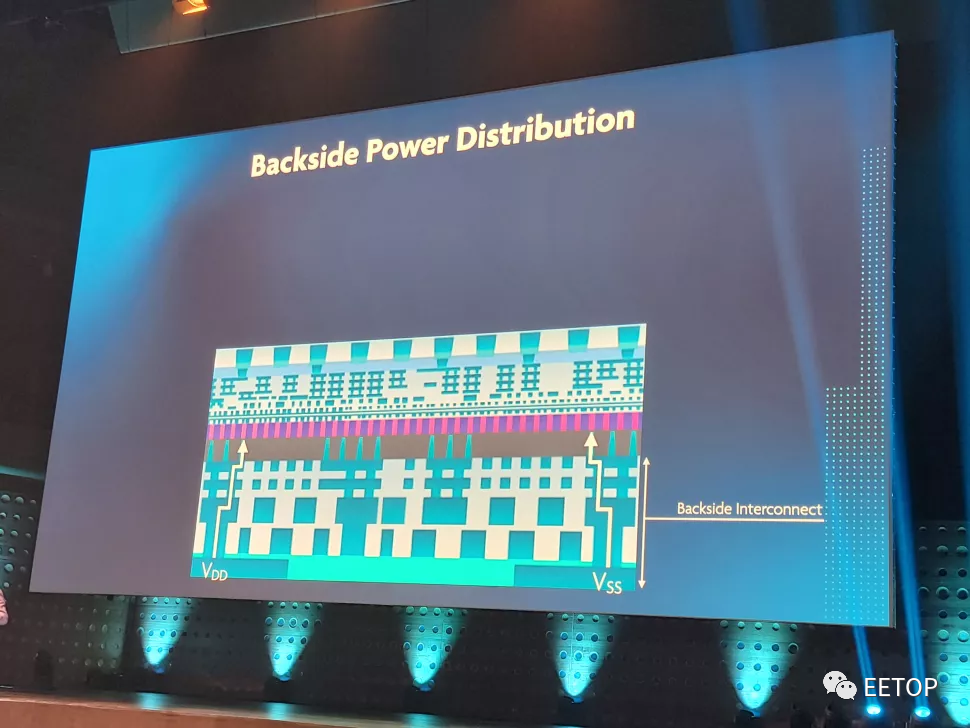

Imec 的 BEOL?'Scaling Boosters' 路线图