Chiplet处理器的最大挑战

1965 年,戈登·摩尔假设微芯片上的晶体管数量大约每两年翻一番。过去几十年表明这是一个准确的预测,因为每个新发布的芯片上都封装了更多的晶体管,并且节点尺寸急剧缩小。

尽管如此,在不对器件功能产生负面影响的情况下,半导体节点尺寸可以变得多么小是有限度的。根据麻省理工科技评论,半导体行业已经承认工艺节点尺寸将很快停止缩小——我们所知道的摩尔定律将终结。

有效回避此节点大小限制的一种有前途的方法是芯片级异构集成。这意味着在一个封装中连接几个专用的、更小的半导体器件,以创建系统级封装 (SiP),而不是片上系统 (SoC)。通过将芯片的功能拆分为称为小芯片的较小设备,半导体制造商可以获得比单片 SoC 更高的产量。

近年来,随着基于小芯片的处理器(例如 AMD 的 Zen 2)越来越受欢迎,行业研究和开发的重点是提高异构架构中的芯片到芯片互连能力。

SiP小芯片架构的兴起

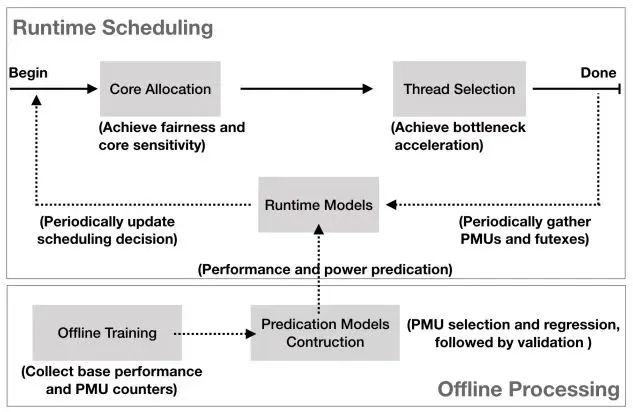

除了提高良率外,异构小芯片架构还允许制造商通过在单个封装中组合不同类型的内核来创建优化的处理器。例如,异构移动处理器可以在单独的小芯片上同时具有高性能、高功耗的内核和低性能、低功耗的内核。这允许称为调度程序的操作系统程序确定哪些程序(线程)专用于每种类型的内核并优化整体功率和性能。

即便如此,基于小芯片的设计也有其自身的技术挑战。SiP 小芯片架构的主要障碍之一是构建具有成本效益、高性能和节能的裸片到裸片互连。

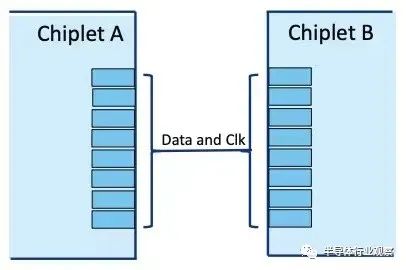

用于芯片间通信的并行互连

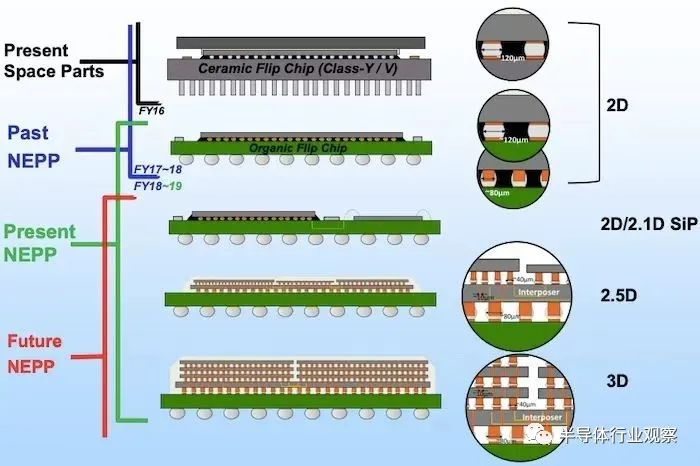

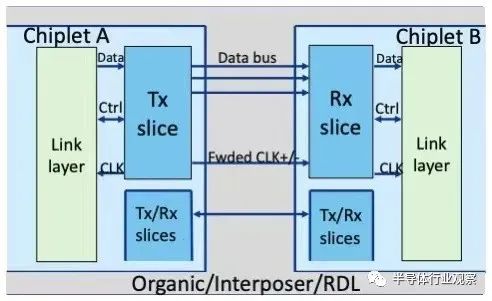

与其他系统一样,有两种广泛类型的物理层裸片到裸片互连:并行和串行。并行和串行互连都具有重要的优势,并且根据 SiP 的几何形状使用。通常,存在三种类型的 SiP 几何形状:2D、2.5D 和 3D。

从历史上看,基于小芯片的架构和 SoC 架构通常使用 2D 封装几何形状。对于这样的几何结构,两个小芯片可能相距较远,串行 SerDes PHY 通常与仅使用一根线传输的时钟和数据一起使用。

SerDes 是一个串行器/解串器系统。该系统从一个小芯片接收并行时钟和数据信号,将其串行化为单线,并以非常高的数据速率将其通过基板传输到另一个小芯片。这对于较长的传输距离(例如 2D 几何 SiP 系统中的传输距离)很有用,因为它消除了并行互连中出现的时钟和数据线之间的时序偏差。本文中的时序偏差是指由于传输线中的传播延迟,数据和时钟信号到达接收器的时间差异。

然而,SerDes 互连是有代价的:由于串行数据和时钟以及随后在接收器上恢复这两个信号所需的复杂电路,它们通常会消耗更多功率。

为了解决这个问题,半导体设计公司已经开始研究使用并行互连和中介层的 2.5D 和 3D 小芯片几何结构。中介层允许小芯片堆叠并大大减少数据和时钟信号需要在小芯片之间传输的距离。此外,中介层还允许非常高密度的并行连接。

因为 2.5D 和 3D 几何结构通过垂直堆叠减少了die之间的距离,所以时序偏差不会像在 2D 几何结构中那样成为问题。因此,并行互连提供了功率效率的最佳组合,同时仍然能够匹配 2D 几何图形中使用的 SerDes 方法的带宽。

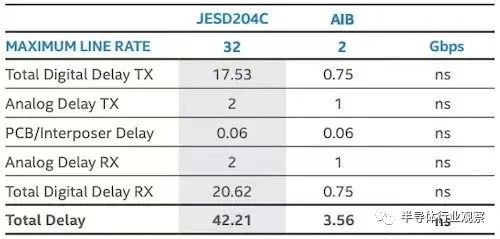

此外,并行互连还可以实现低得多的延迟传输,因为不再有与 SerDes 系统中的序列化、反序列化、编码和解码相关的任何开销。事实上,英特尔已经证明其高级接口总线 (AIB) 标准与 SerDes 系统相比,总延迟(延迟)要低得多。

标准化 Chiplet 互连协议

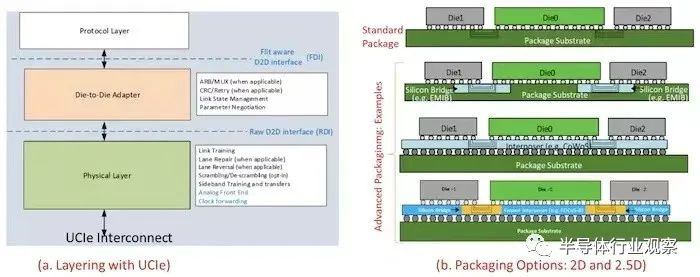

随着高性能计算和机器学习的兴起,异构处理器必须处理的工作负载急剧增加。因此,宣布了一项名为Universal Chiplet Interconnect Express (UCIe)的新协议标准,以帮助在整个半导体行业建立一个开放的小芯片生态系统。UCIe 是一种分层协议,它指定了物理层、die-to-die 适配器层和协议层。它允许 2D 和 2.5D 几何形状用于封装,如下图所示。

UCIe 力求成为整个半导体行业使用的节能和成本效益标准,并可能在未来的异构架构中发挥关键作用。