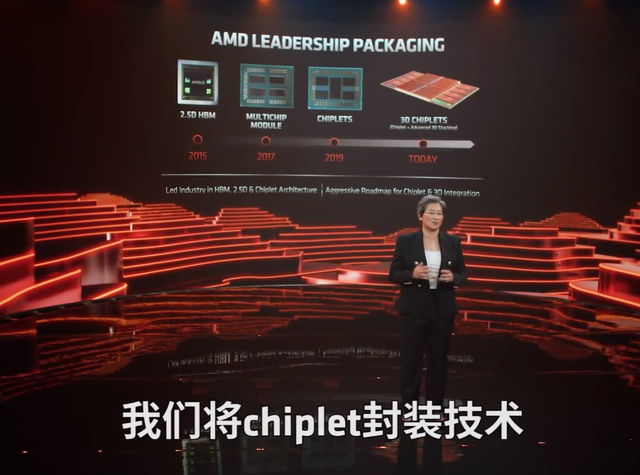

AMD 官宣 3D Chiplet 架构:可实现“3D 垂直缓存”

6 月 1 日消息 在今日召开的 2021 台北国际电脑展(Computex 2021)上,AMD CEO 苏姿丰发布了 3D Chiplet 架构,这项技术首先将应用于实现“3D 垂直缓存”(3D Vertical Cache),将于今年年底前准备采用该技术生产一些高端产品。

本文引用地址:http://www.eepw.com.cn/article/202203/432001.htm

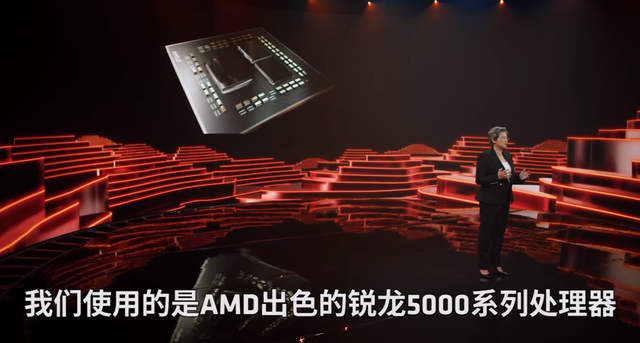

苏姿丰表示,3D Chiplet 是 AMD 与台积电合作的成果,该架构将 chiplet 封装技术与芯片堆叠技术相结合,设计出了锐龙 5000 系处理器原型。

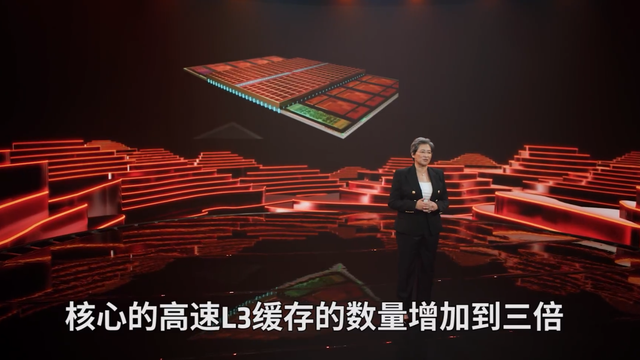

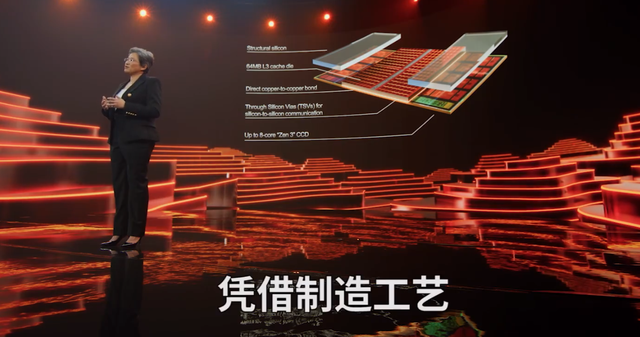

官方展示了该架构的原理,3D Chiplet 将一个 64MB 的 7nm 的 SRAM 直接堆叠在每个核心复合体之上,总而将供给“Zen 3”核心的高速 L3 缓存数量增加到 3 倍。

3D 缓存直接与“Zen 3”的 CCD 结合,通过硅通孔在堆叠的芯片之间传递信号和功率,支持每秒超过 2TB 的带宽。

3D Chiplet 架构的处理器与目前的锐龙 5000 系列外观上完全相同,官方展示了一个 3D Chiplet 架构的锐龙 9 5900X 原型(为了方便展示,官方拆了盖子)。

苏姿丰称,在实际设备中,一个单独的 SRAM 将与每一块 CCD 结合,每块 CCD 可获得的缓存数量为 96MB,而或在单个封装中的 12 核或 16 核处理器总共可获得 192MB 的缓存。