台积电公布更多3nm细节 预计2022年量产

在台积电的年度技术研讨会上,详细介绍了未来3nm工艺节点的特点,并为5nm的后续产品规划了路线图,包括N5P和N4工艺节点。

从台积电即将推出的N5进程节点开始,它代表了继很少使用的N7+节点(例如麒麟990 SoC使用)之后的第二代深紫外(DUV)和极紫外(EUV)节点。台积电(TSMC)已经开始量产几个月了,苹果的下一代soc可能是该节点的首批候选产品。

台积电详细介绍说,N5目前的缺陷密度比N7改善了四分之一,新节点在量产时的良率高于其前身的主要节点N7和N10,预计缺陷密度将继续改善,超过过去两代的历史趋势。

代工厂同时正在准备一种新的N5P节点,它基于当前的N5工艺,可提高5%的速度并减少10%的功耗。

除了N5P之外,台积电还引入了N4节点,它代表了N5工艺的进一步发展,采用了更多的EUV层来减少掩模,而芯片设计者所需的迁移工作最少。我们将看到N4 风险生产将于2021年4季度开始,并在2022年晚些时候批量生产。

今天最大的新闻是台积电披露了他们下一代跨越N5进程节点家族,3纳米工艺N3,去年就开始着手定义该节点,目前进展顺利。

与三星3nm工艺节点使用GAA(Gate all around)晶体管结构相反,台积电将坚持使用FinFET晶体管,并依靠“创新功能”来实现N3承诺的全节点扩展。

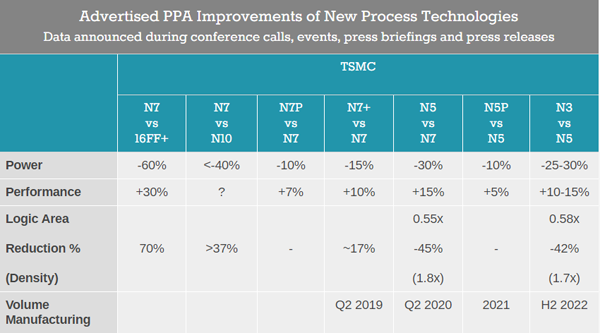

新工艺技术的PPA改进

与N5节点相比,N3承诺在相同的功率水平下可以提高10-15%的性能,或者在相同的晶体管速度下降低25-30%的功率。此外,台积电承诺逻辑面积密度提高1.7倍。当然这种收缩并不能直接针对所有结构,SRAM的密度仅得到20%的改善,而模拟结构会改善得更小。

现代芯片设计非常注重SRAM,一般情况下SRAM与逻辑占比为70/30,因此在芯片级别上,预期的收缩率仅为26%或更少。

N3计划在2021年进入风险生产,并在2022年下半年进入批量生产。台积电在N3上披露的工艺特性将与三星在3GAE上披露的功率和性能差别不大,但在密度方面将领先更多。